微机原理学习记录

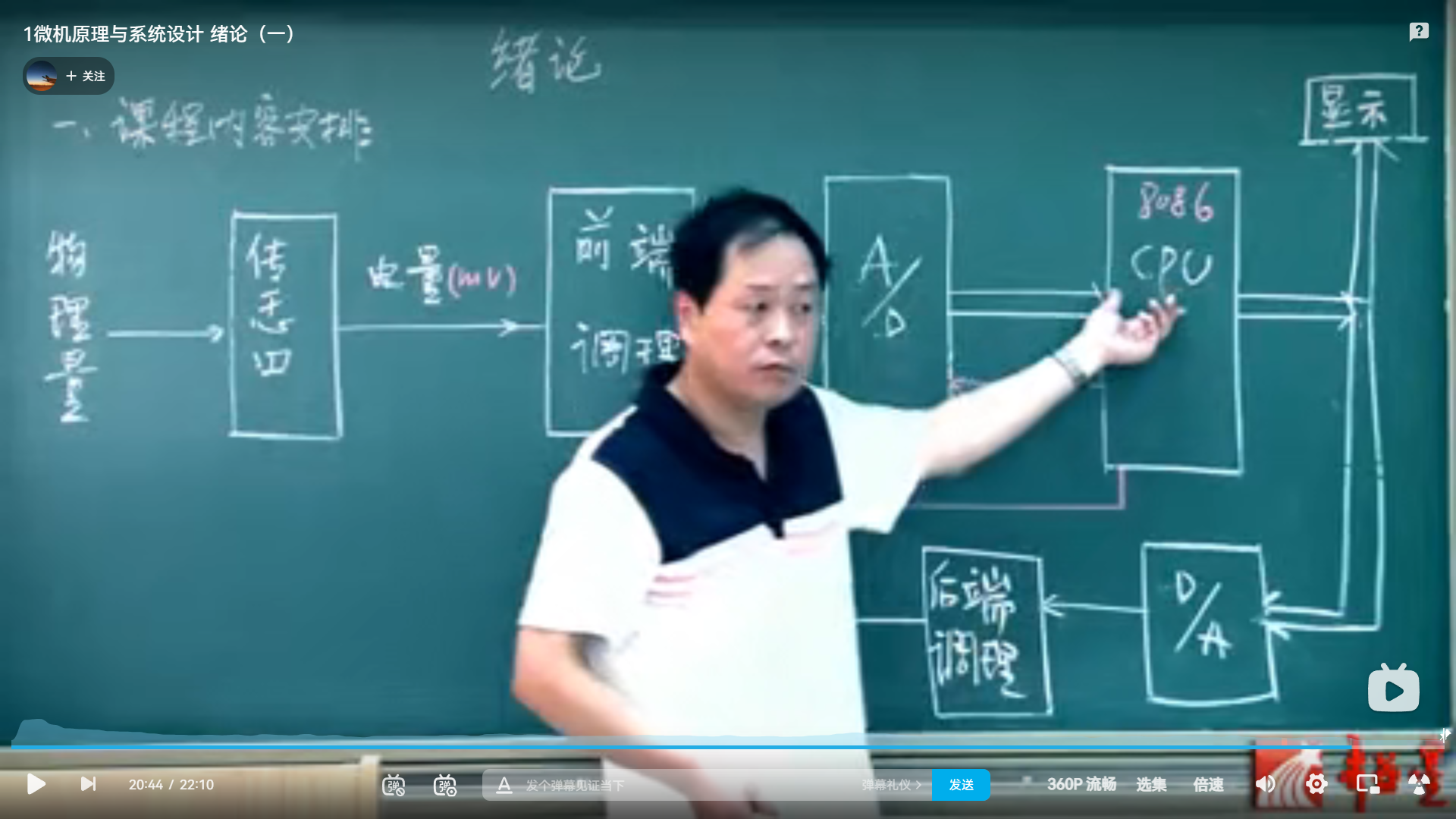

绪论(一)

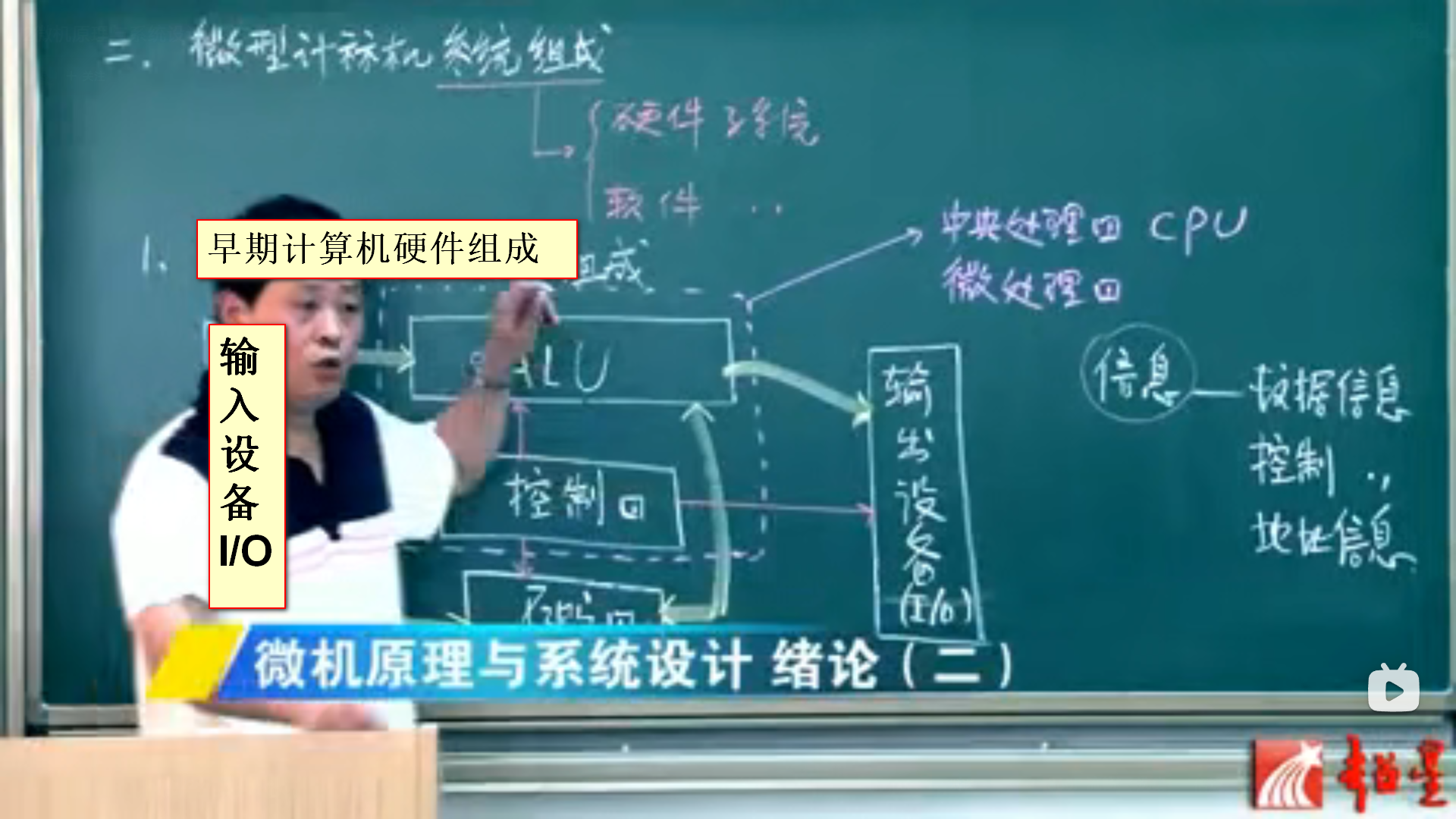

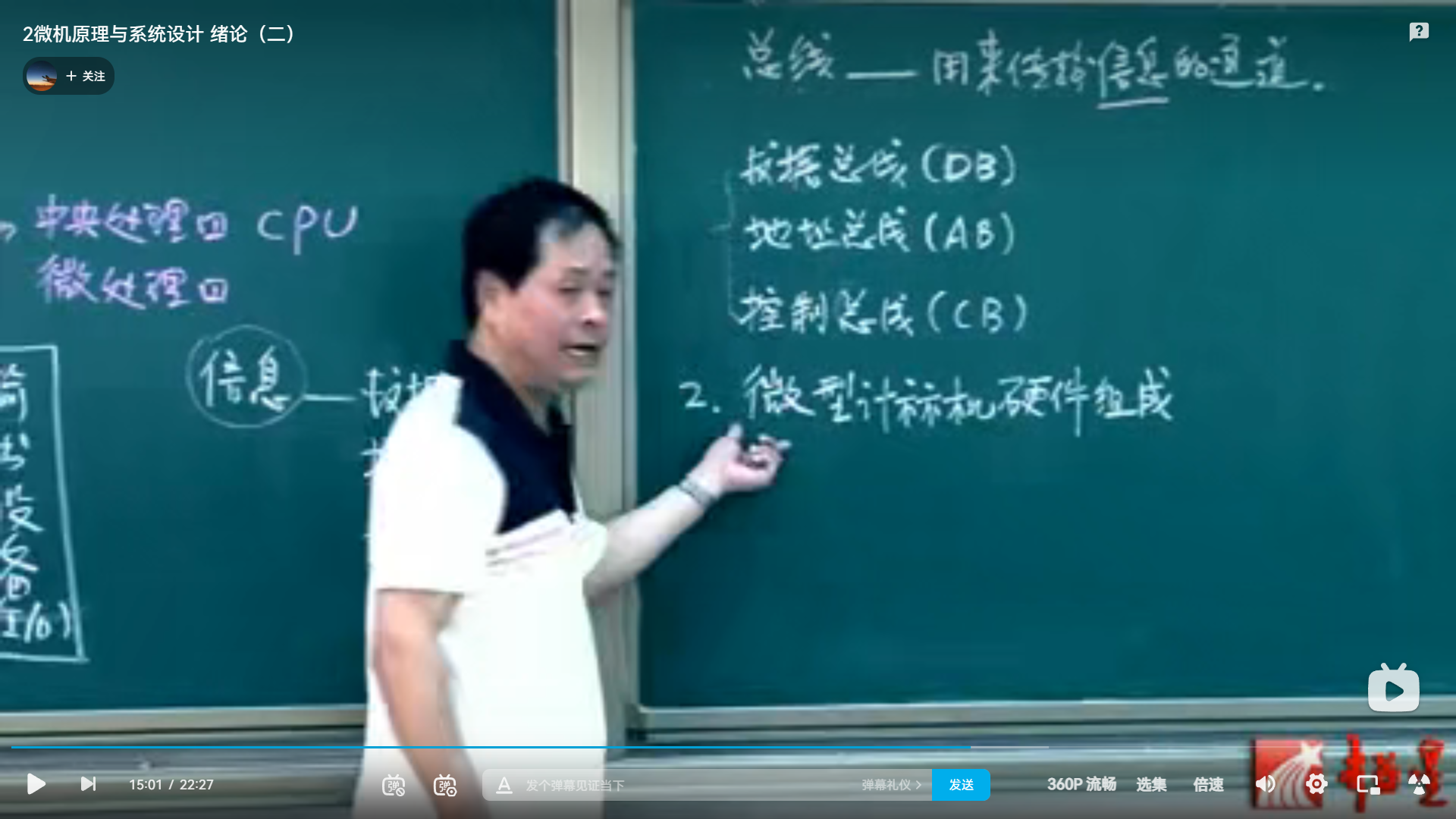

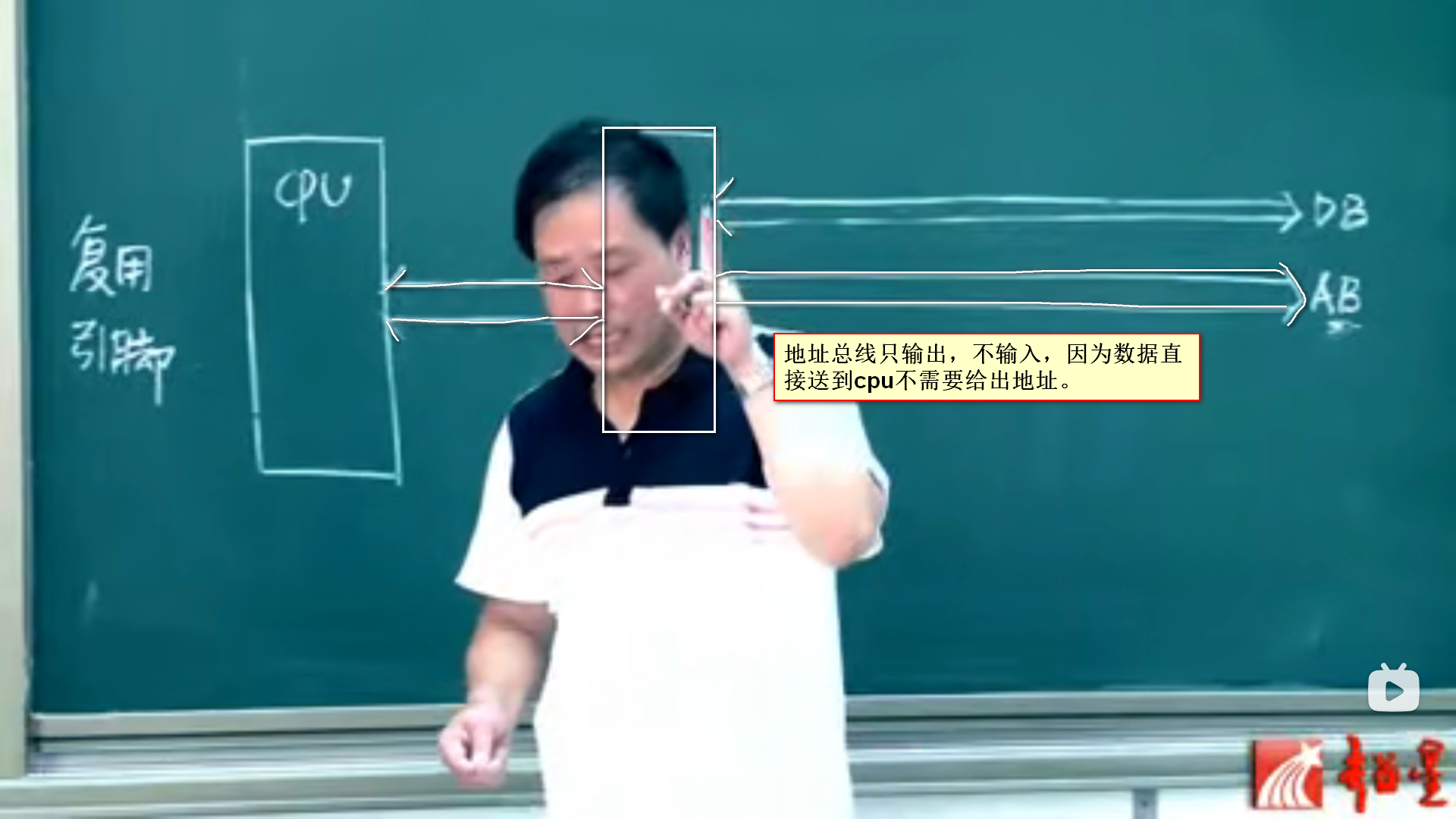

绪论(二)

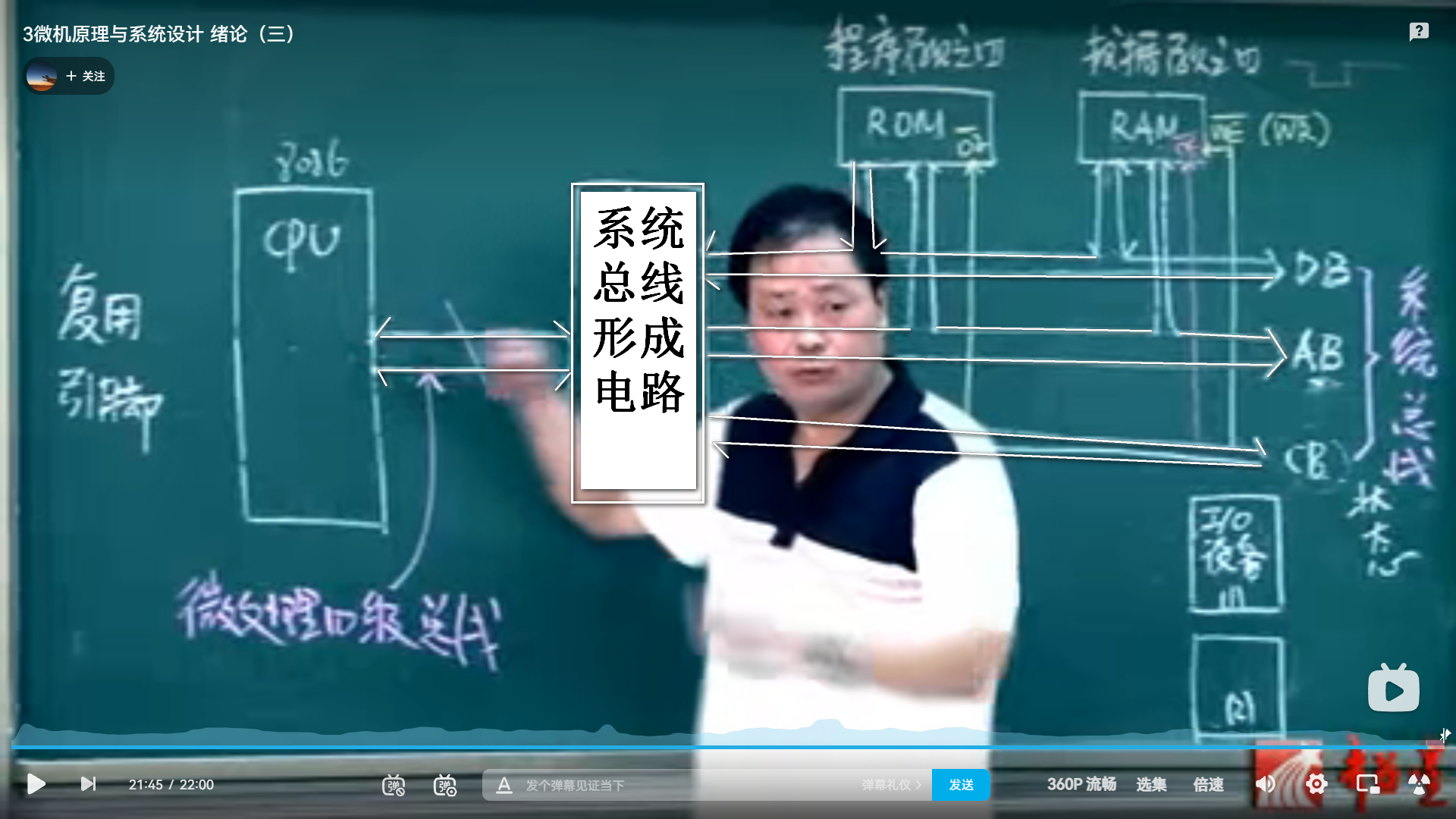

绪论(三)

- 芯片引脚OE,英文全称为Output Enable,中文意思为输出使能端、输出允许信号。

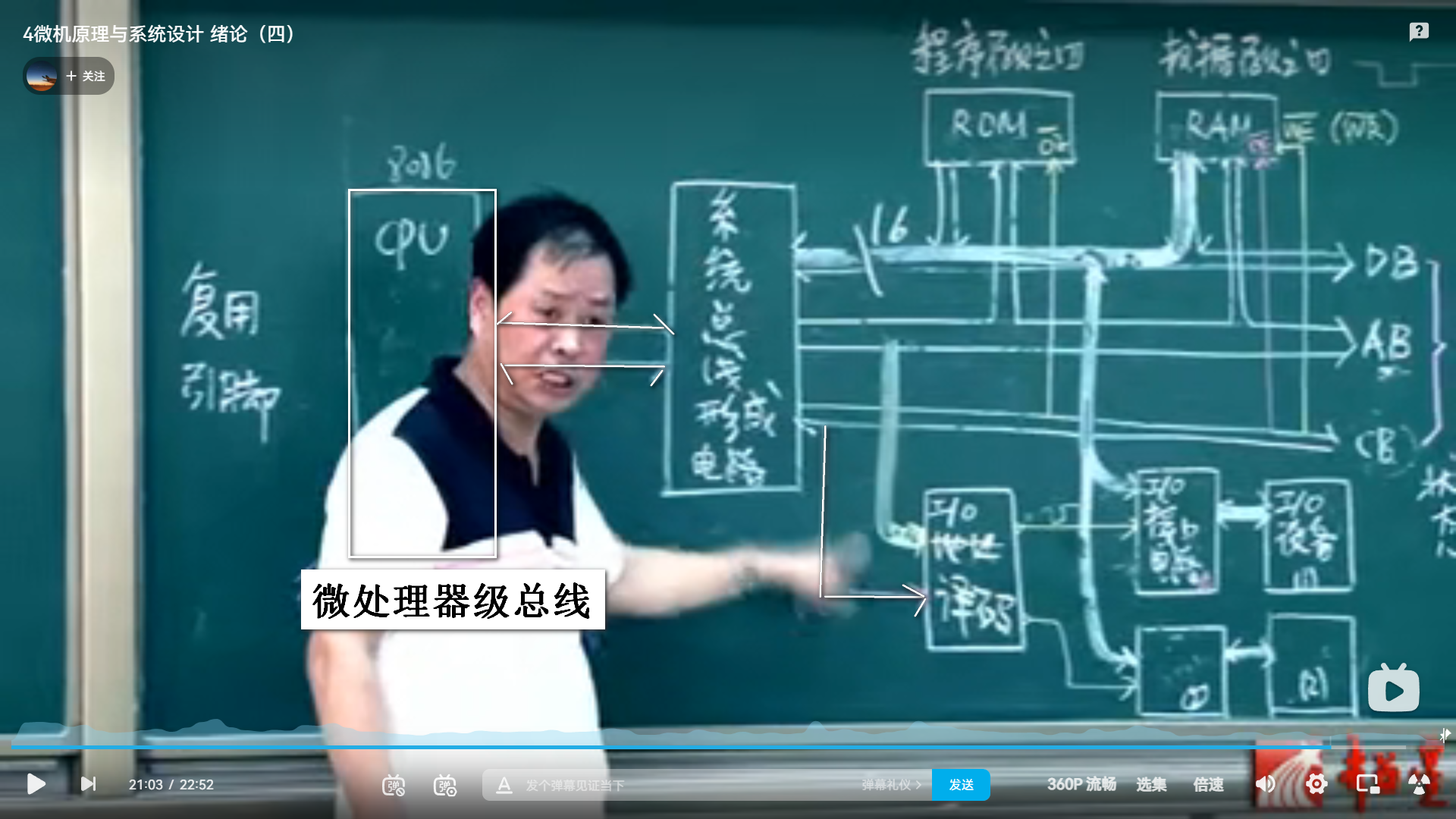

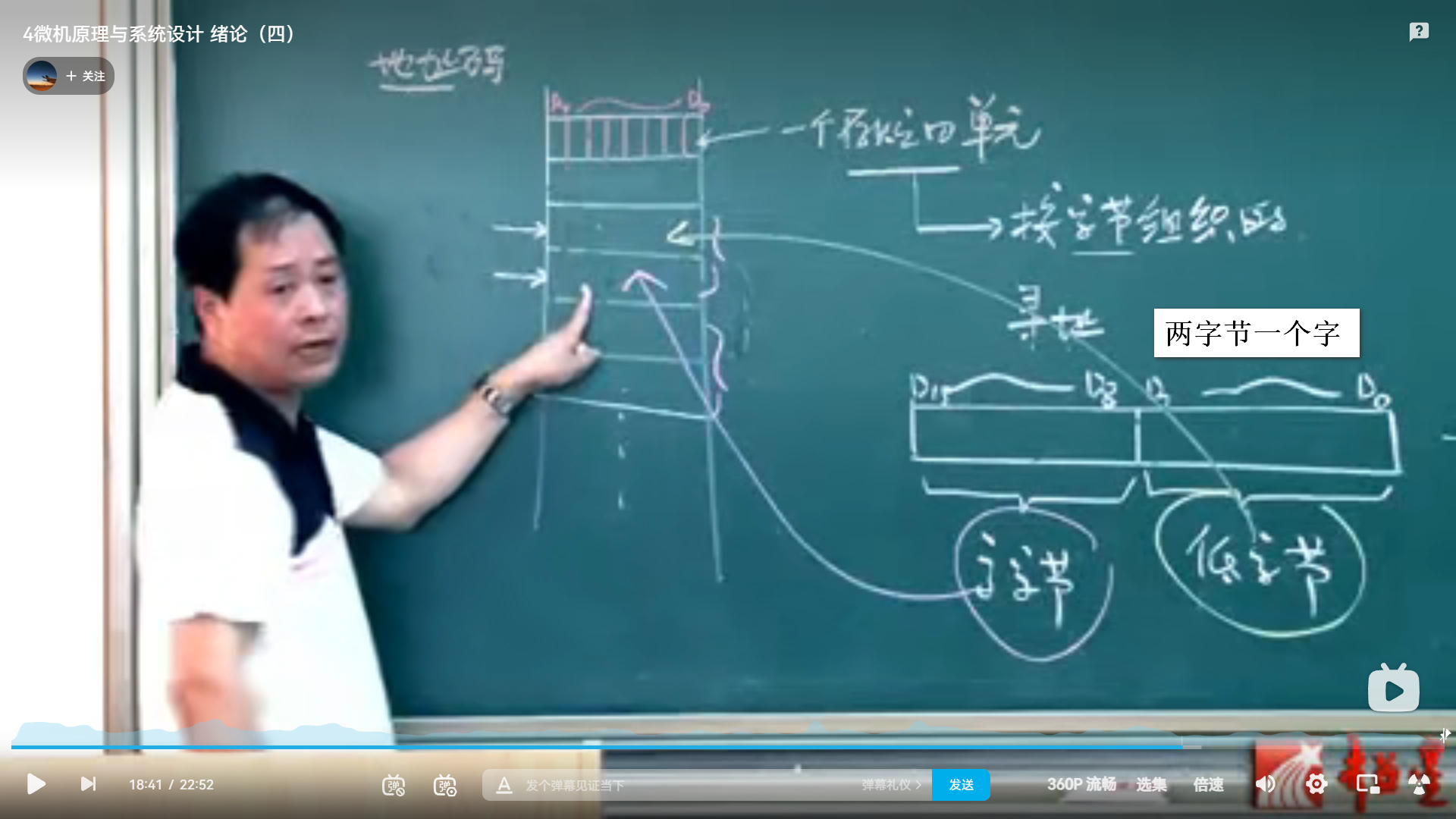

绪论(四)

数制与码制(一)

进制转换

二进制、八进制、十进制、十六进制之间相互转换

-

其他进制转换为十进制

某位上的数字乘上它的权,求其总和。

- 二进制转换为十进制\begin{align} 1\times2^0+1\times2^1+0\times2^2+0\times2^3+1\times2^4+0\times2^5+0\times2^6+1\times2^7\\=1+2+16+128 \\= 147 \end{align}

-

十进制转换成其他进制

-

整数部分转换

-

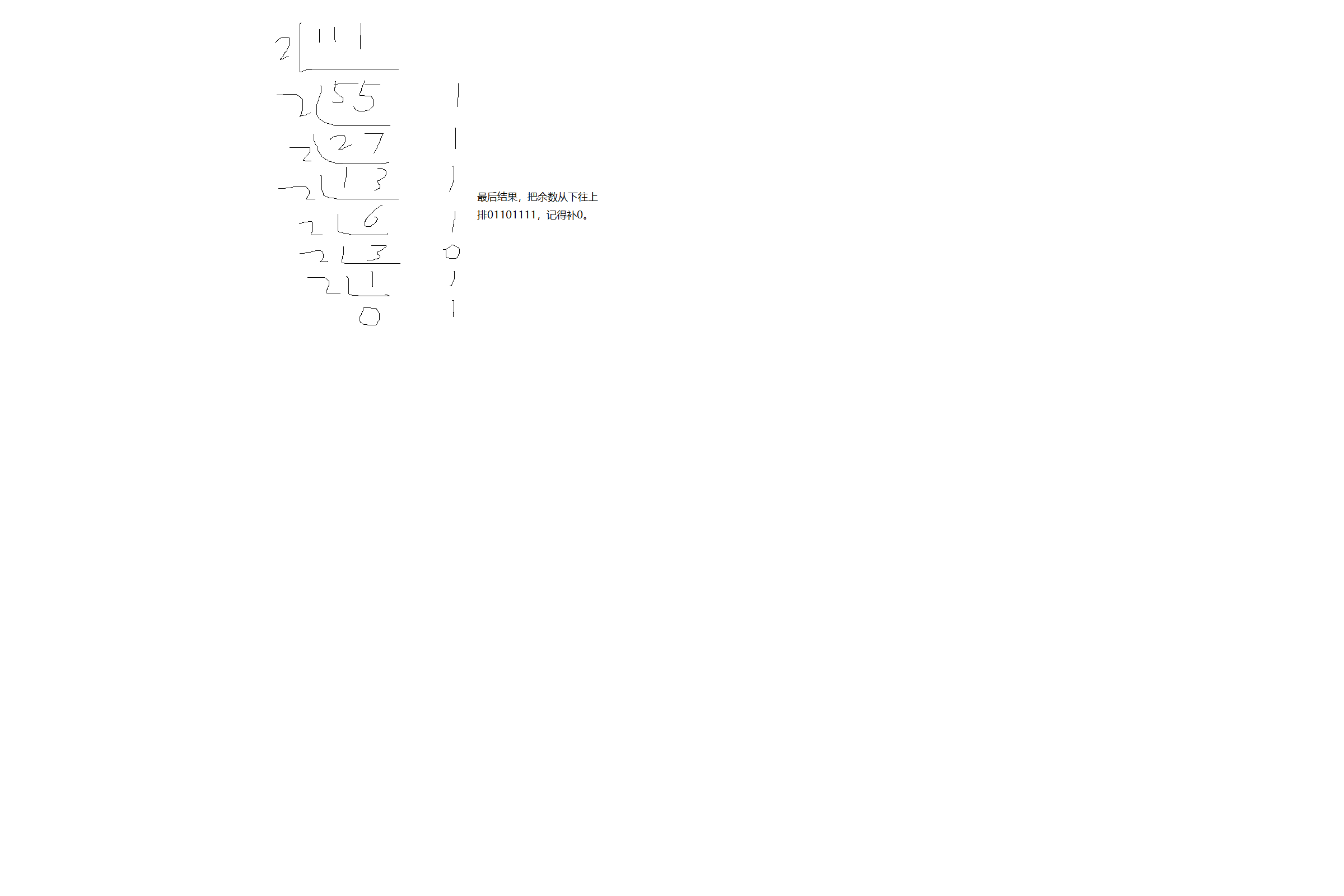

111转换成二进制数

-

-

小数部分转换

-

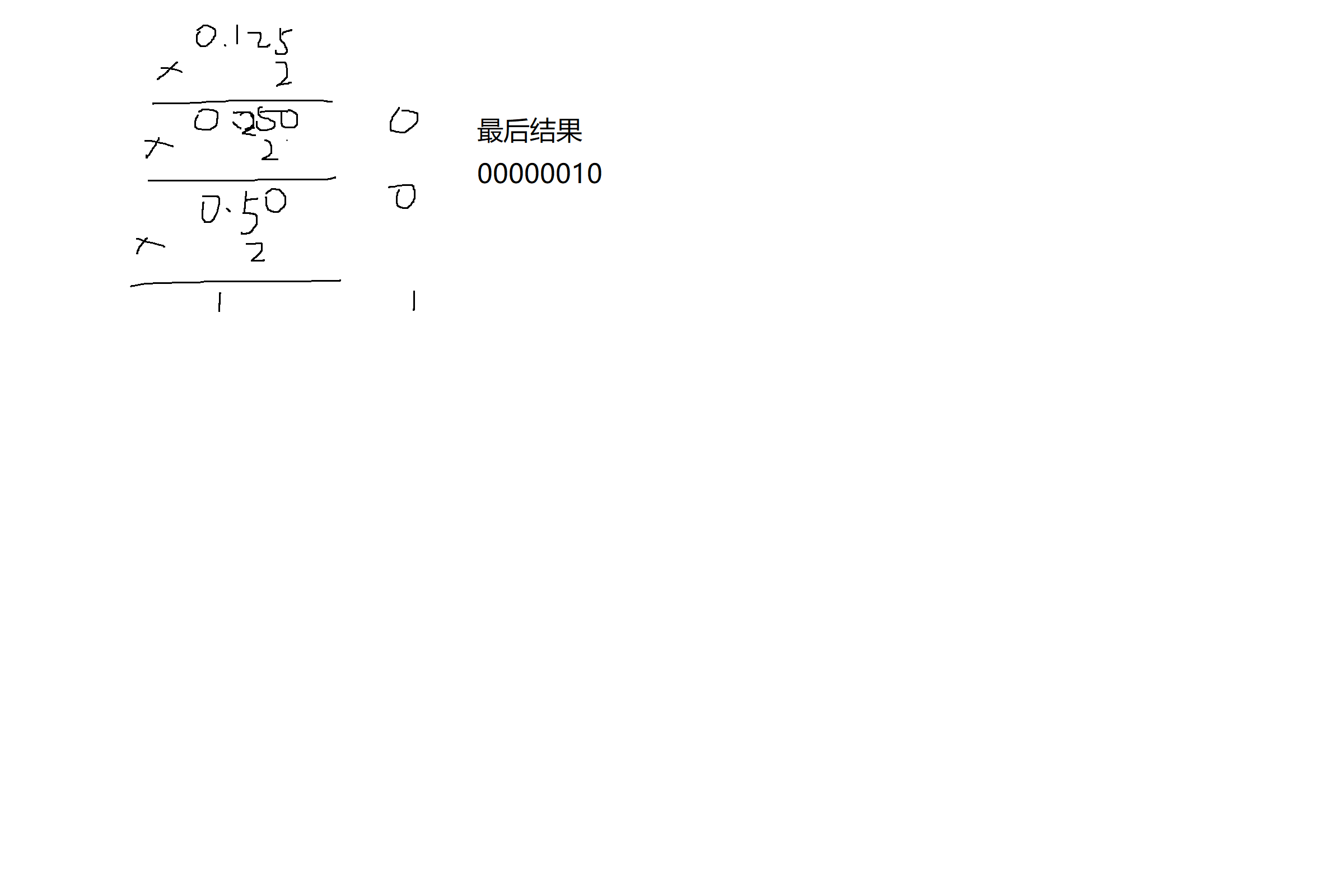

转换成二进制数

-

-

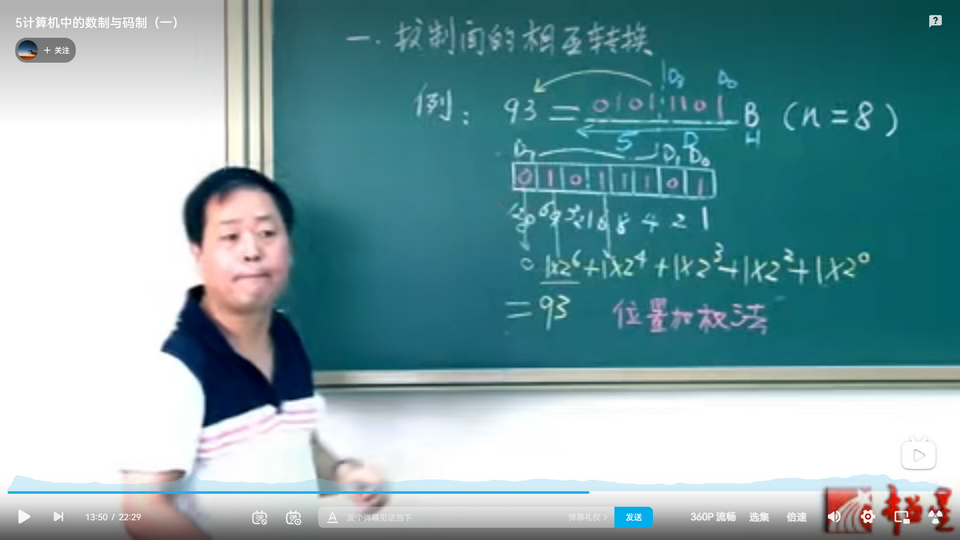

位置加权法

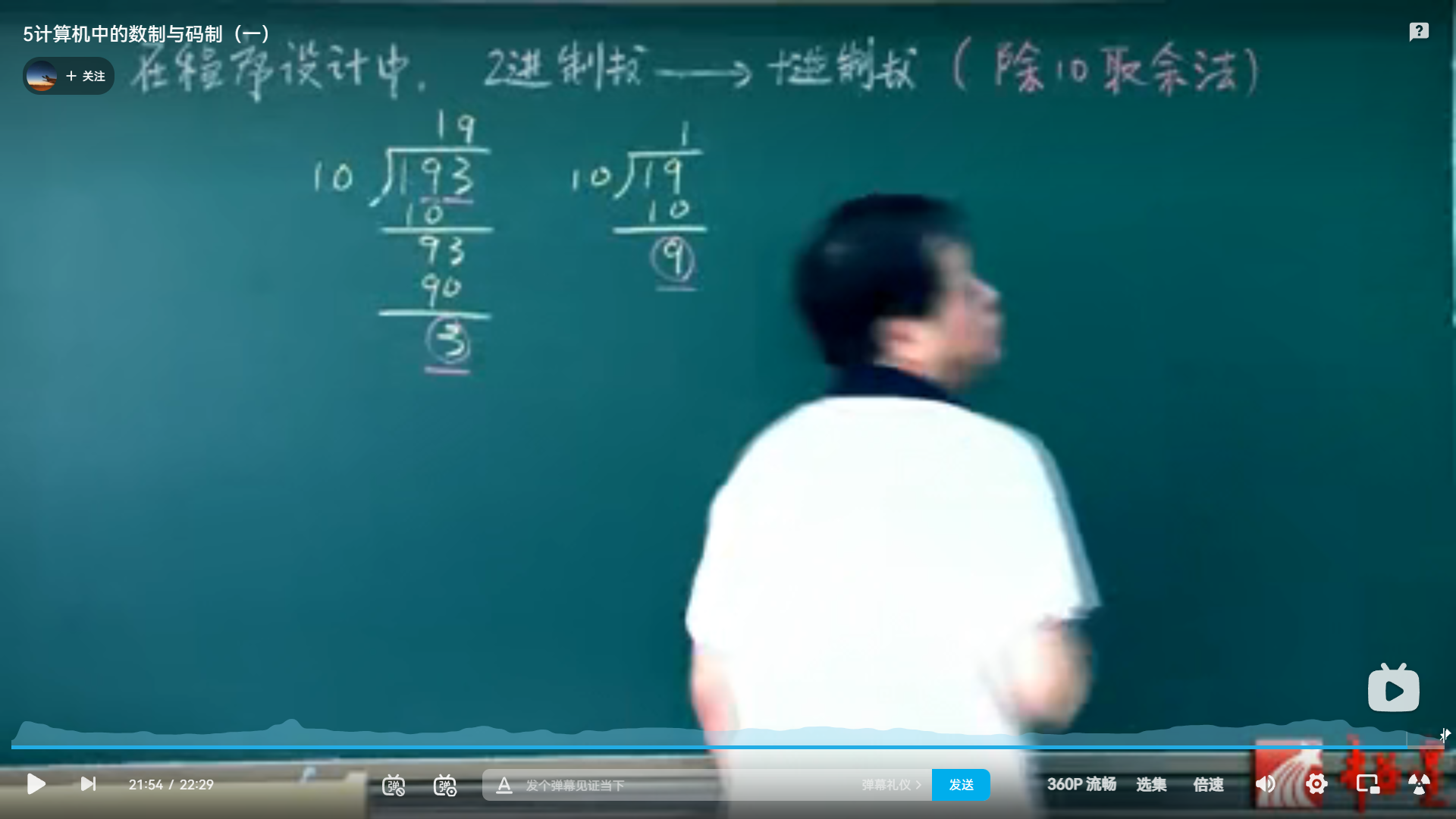

除十取余法

在程序设计中把二进制转化为十进制的一种算法,在手工运算时行不通

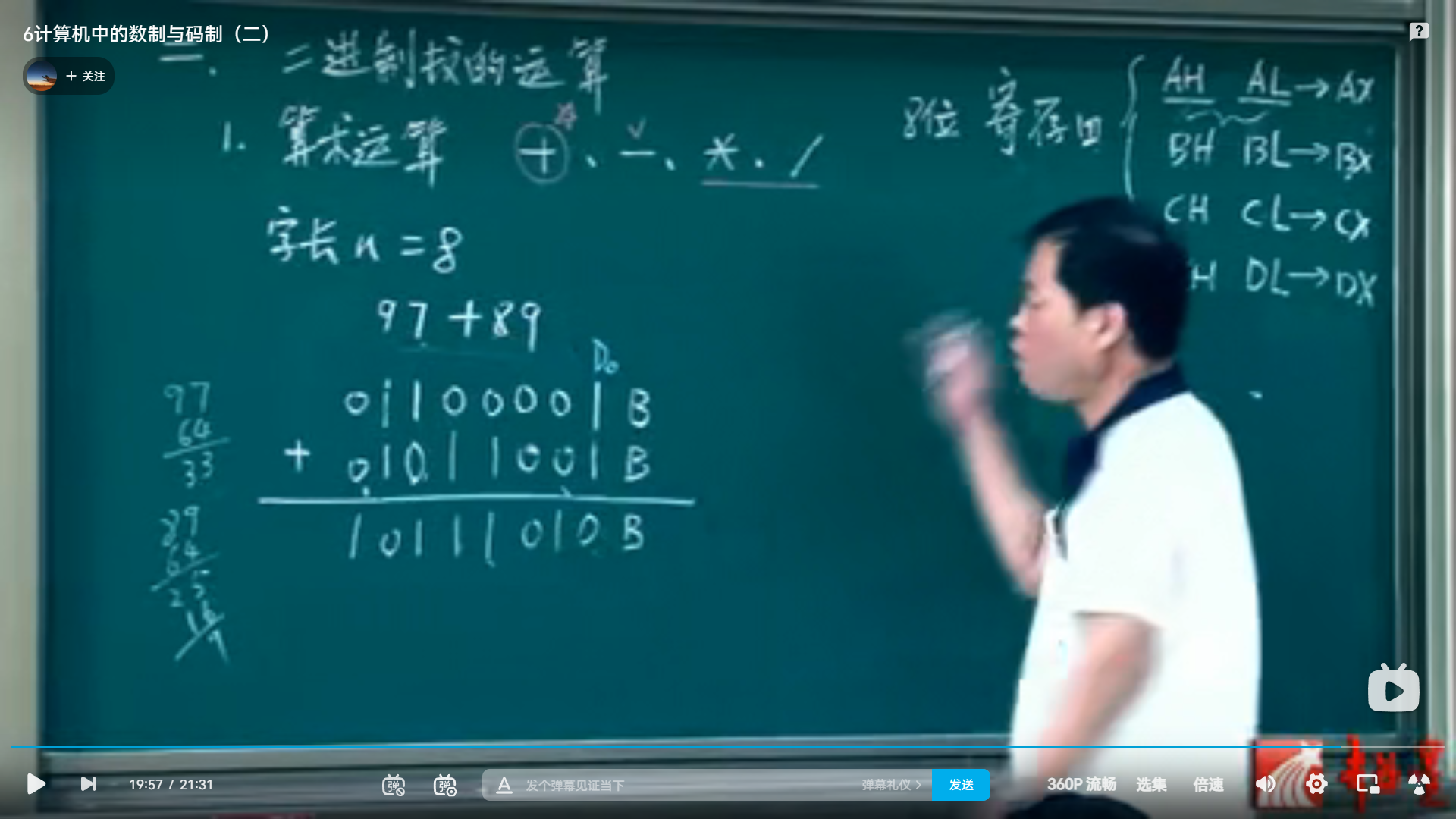

数制与码制(二)

比较法

在程序设计中把二进制转化为十进制的一种算法

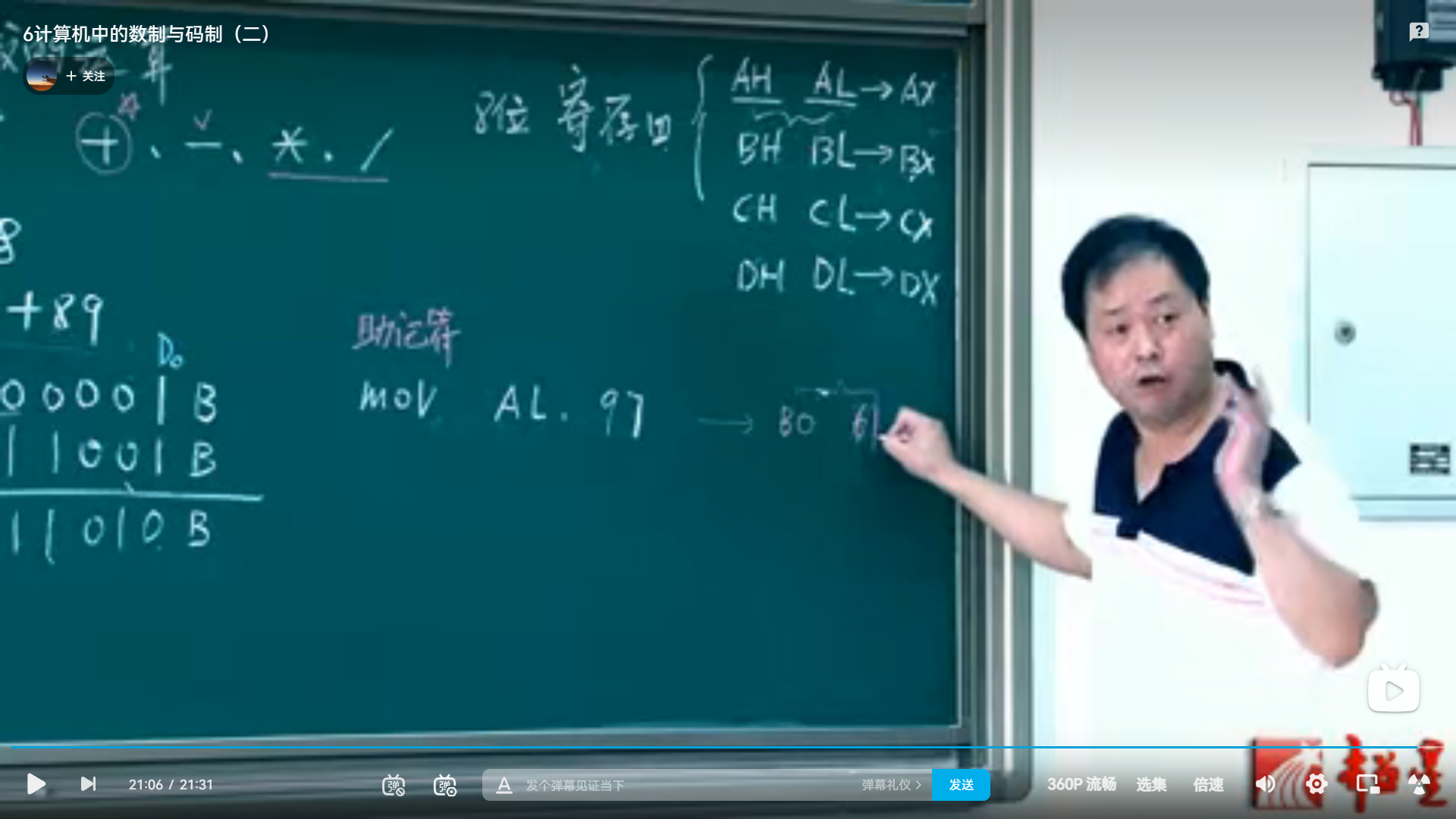

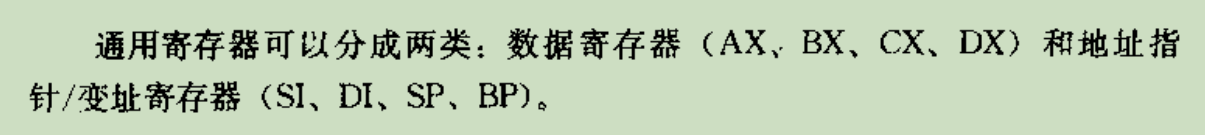

数据寄存器(AX,BX,CX,DX)

数据寄存器有 AX,BX,CX,DX 四个组成,由于在 8086 之前的 CPU 为 8 位 CPU,所以为了兼容以前的 8 位程序,在 8086 CPU 中,每一个数据寄存器都可以当做两个单独的寄存器来使用,由此,每一个 16 位寄存器就可以当做 2 个独立的 8 位寄存器来使用了。

AX 寄存器可以分为两个独立的 8 位的 AH 和 AL 寄存器;

BX 寄存器可以分为两个独立的 8 位的 BH 和 BL 寄存器;

CX 寄存器可以分为两个独立的 8 位的 CH 和 CL 寄存器;

DX 寄存器可以分为两个独立的 8 位的 DH 和 DL 寄存器;

除了上面 4 个数据寄存器以外,其他寄存器均不可以分为两个独立的 8 位寄存器 ;

数制与码制(三)

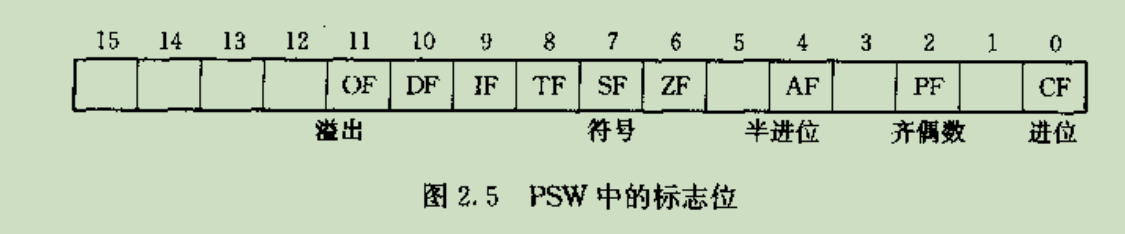

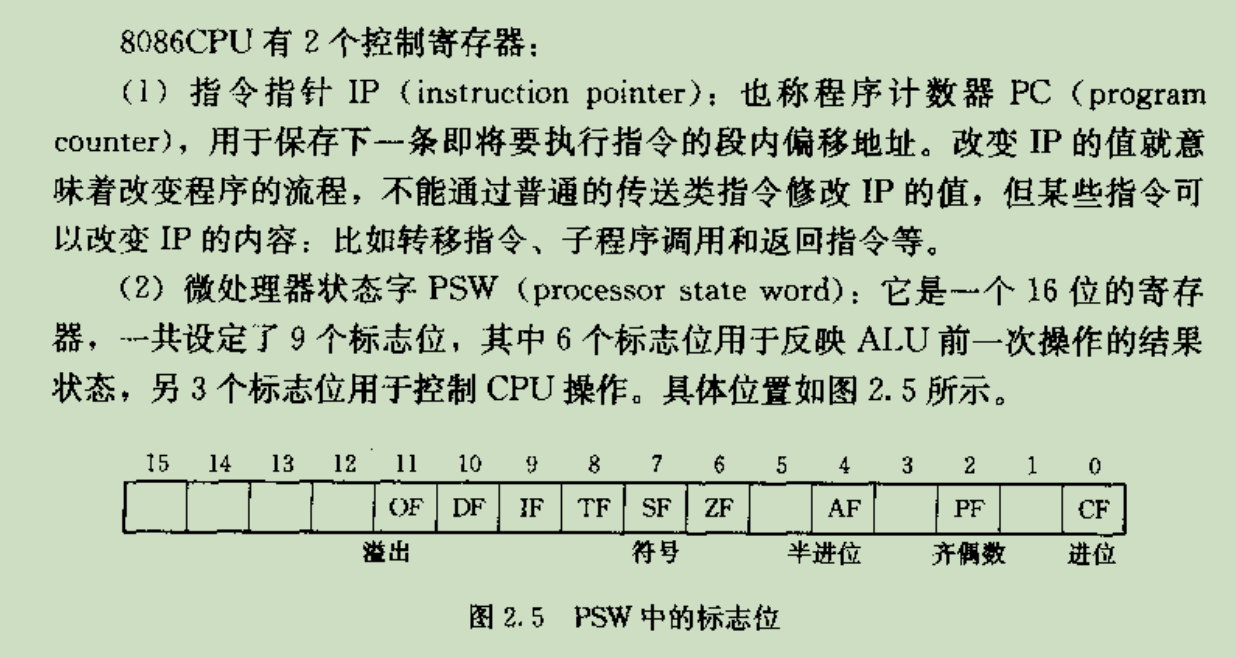

PSW寄存器

进位标志CF(Carry Flag)、奇偶标志PF(Parity Flag)、辅助进位标志AF(Auxiliary Carry Flag)、零标志ZF(Zero Flag)、符号标志SF(Sign Flag)、溢出标志(Overflow Flag)。

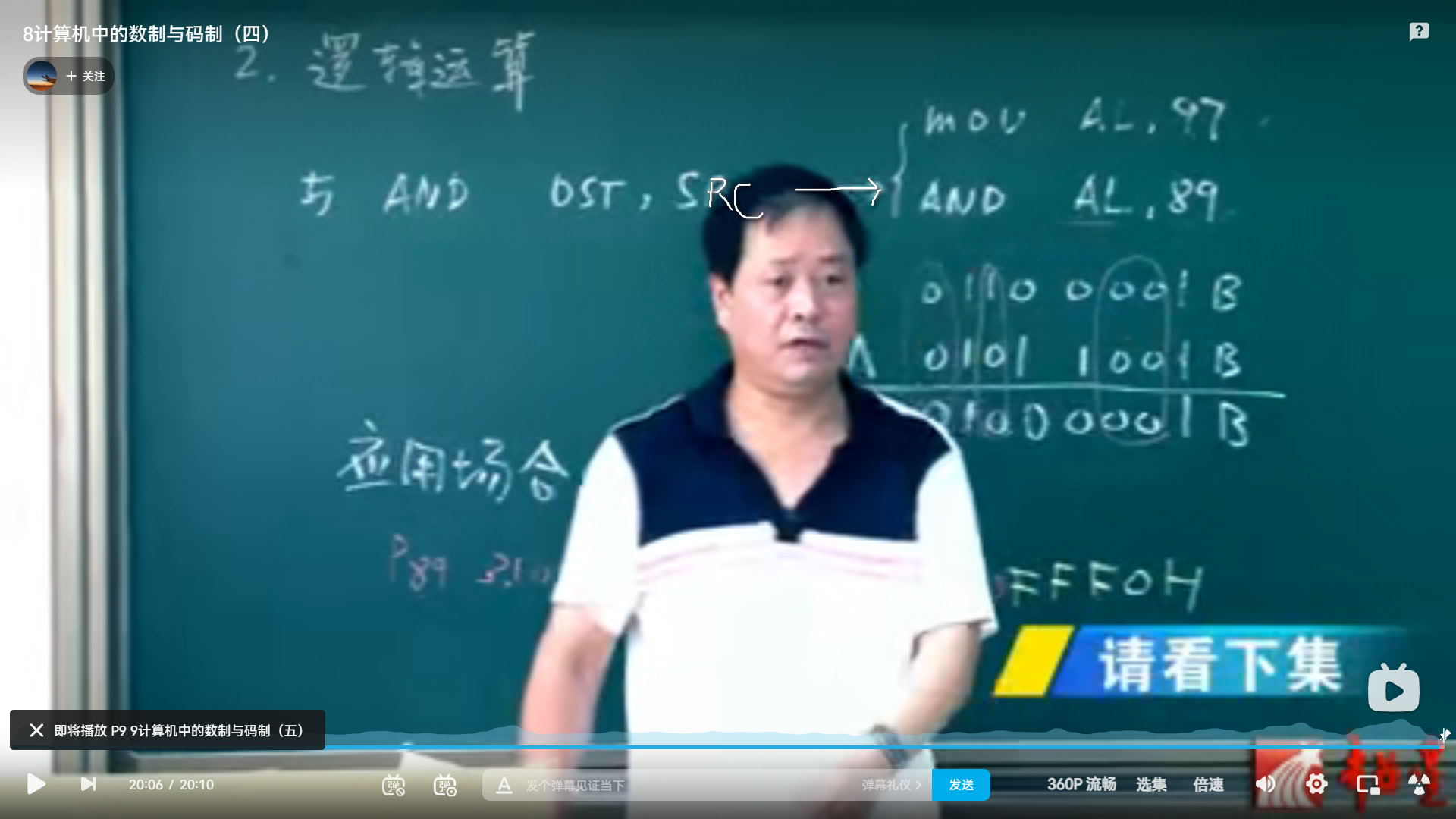

数制与码制(四)

汇编语言——十六进制数据前加0规则

十六进制以A~F打头的数字出现在指令中时,前面一定要加一个数字0,以免与其它符号相混淆。

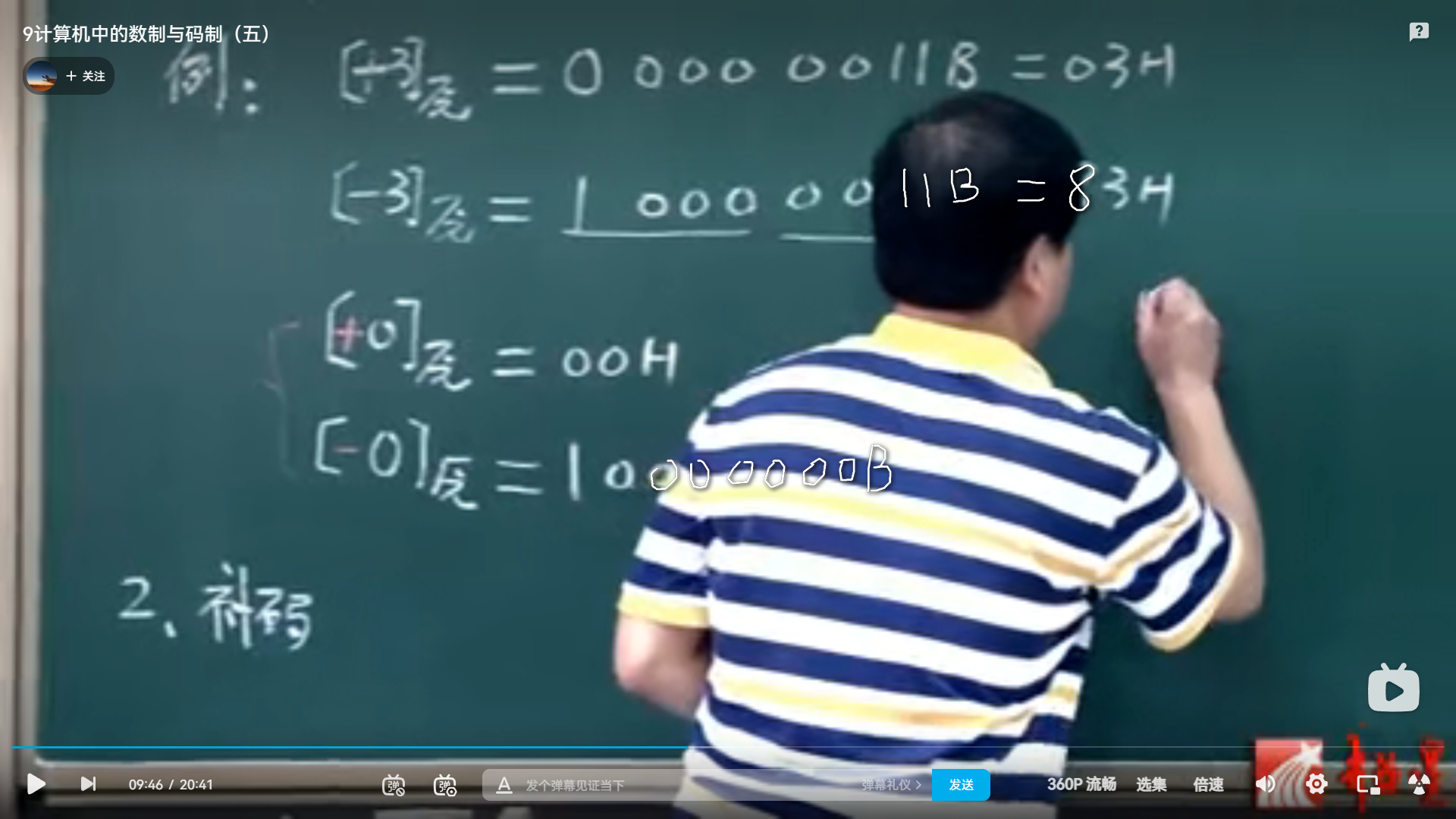

数制与码制(五)

原码

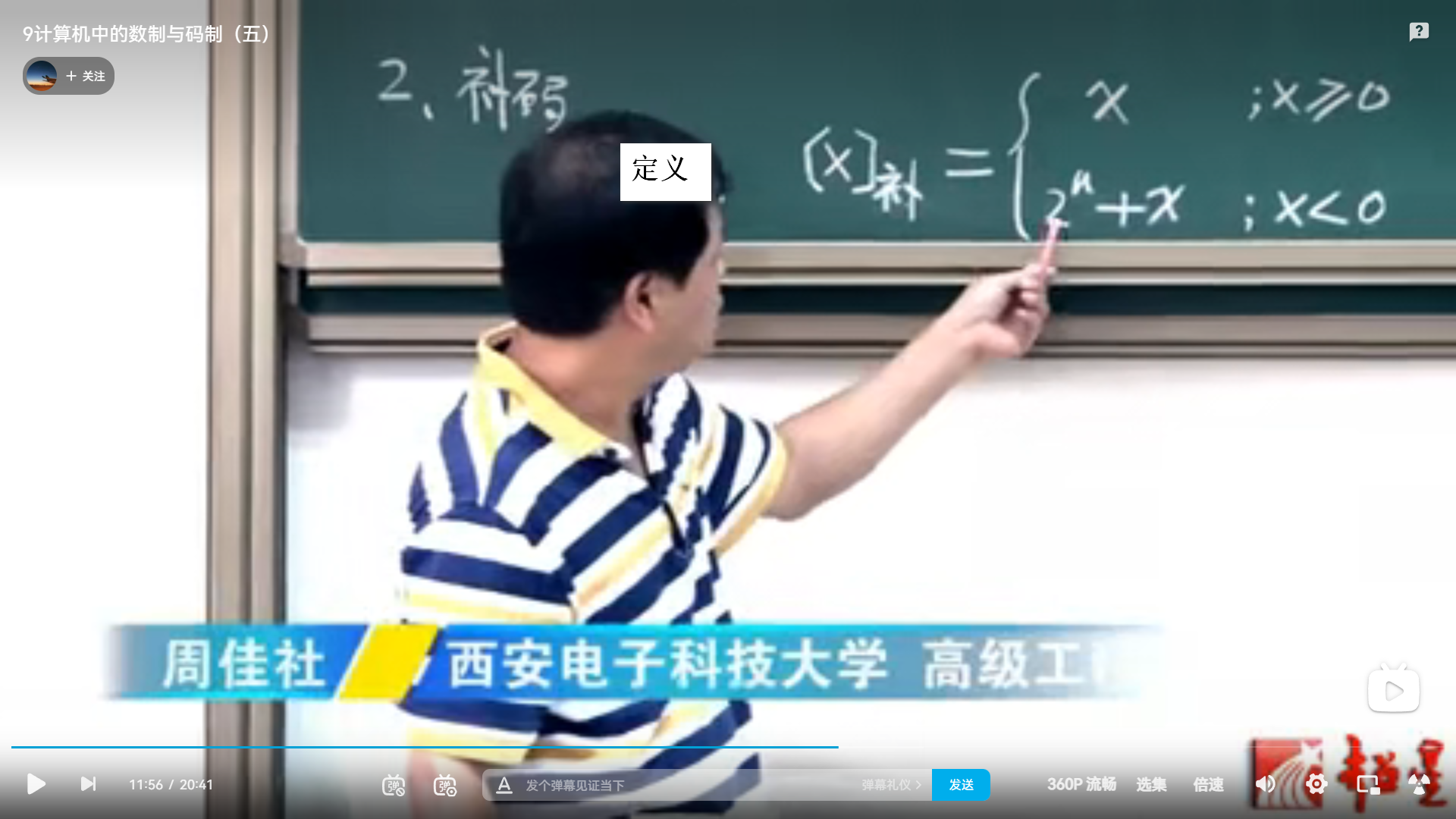

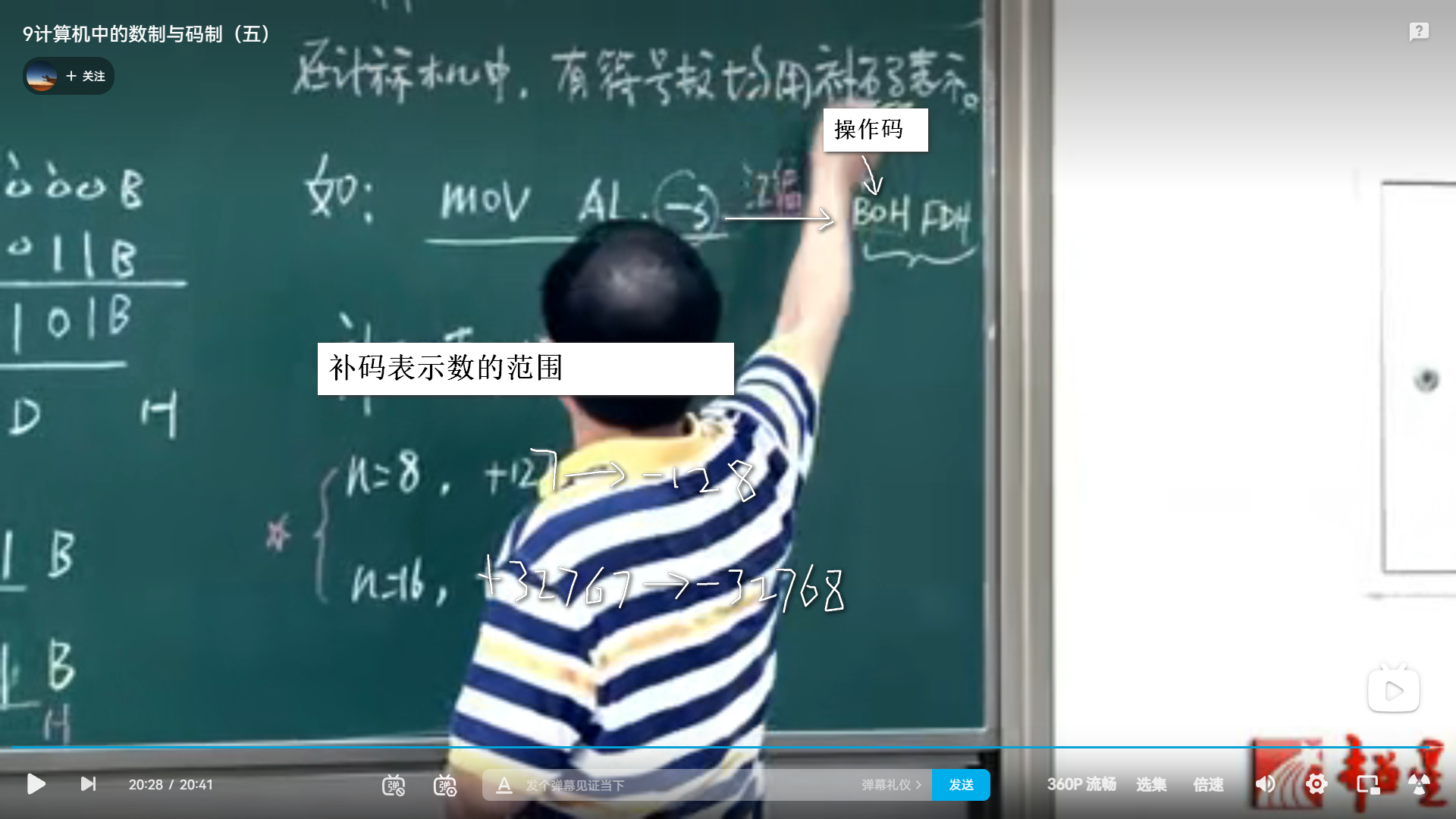

补码

原码除符号位之外各位取反,最后加一就得到补码

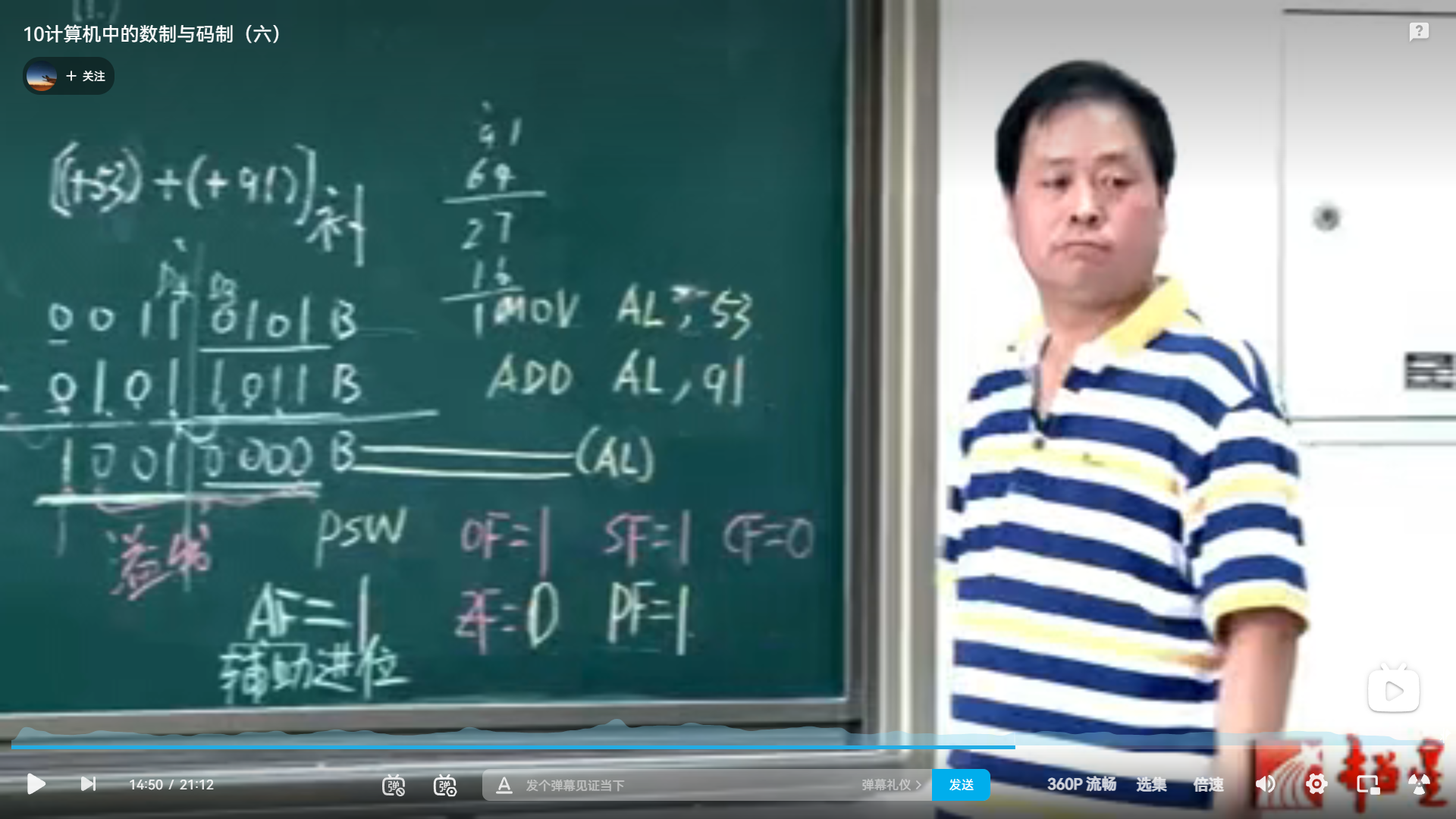

数制与码制(六)

PF:奇偶标志位 (用于数据发送时接收方校验所收数据真实性 , 发送方通过填充奇偶标志位使得发送数据的二进制数的1的个数为奇或为偶)(8086为奇校验)

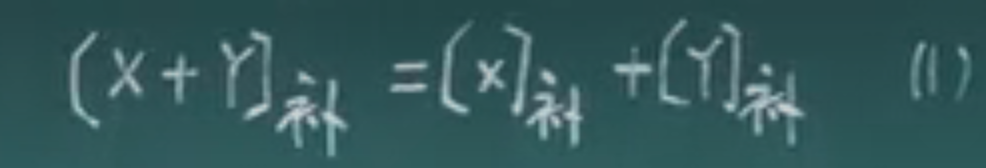

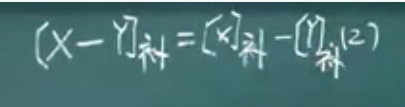

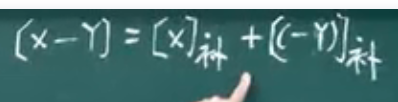

补码运算规则

在计算机中,通常总是用补码完成算术的加减法运算。其规则是:

[X+Y]补= [X]补 + [Y]补 ,[X-Y]补= [X]补 - [Y]补 = [X]补 + [-Y]补

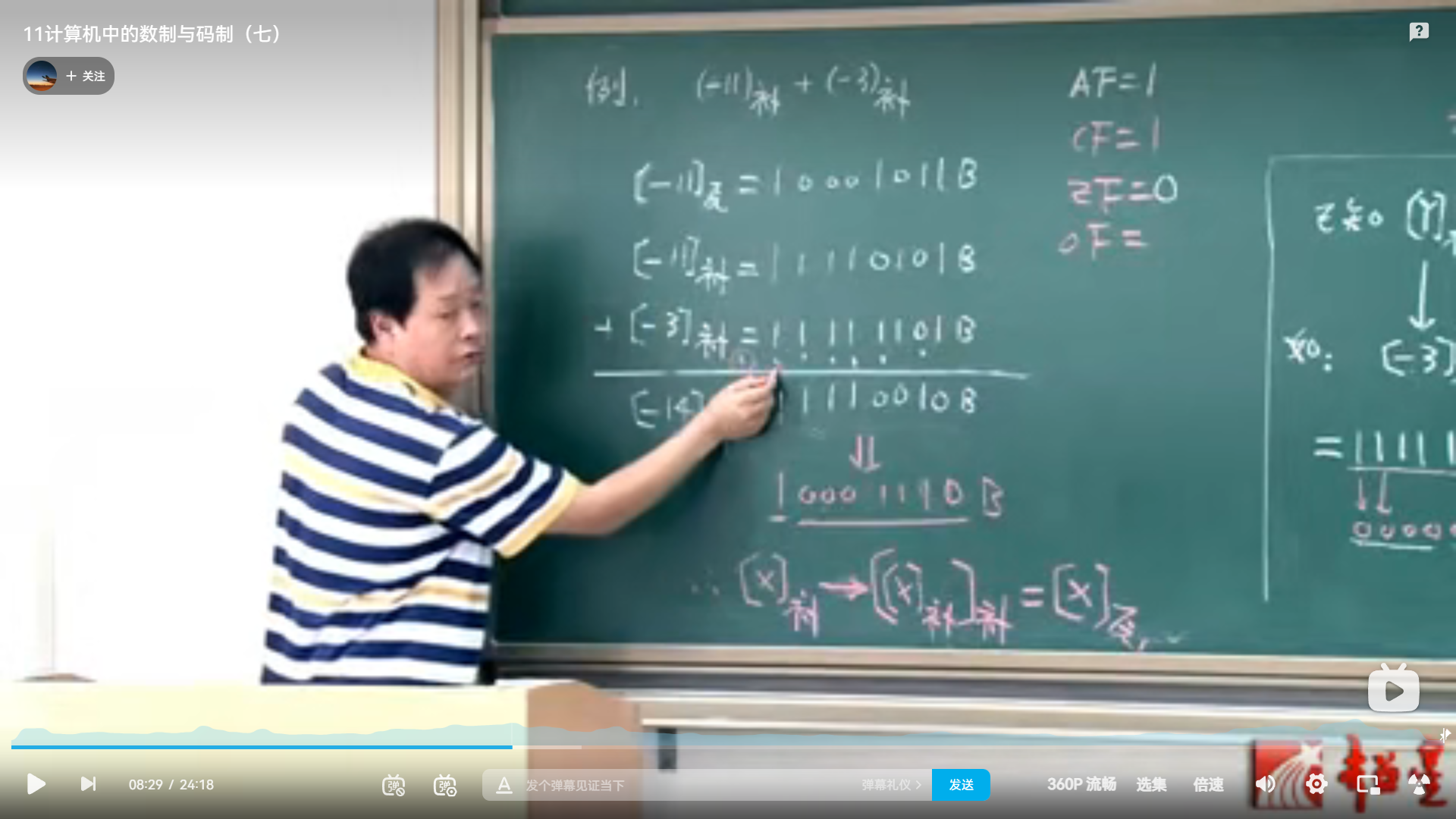

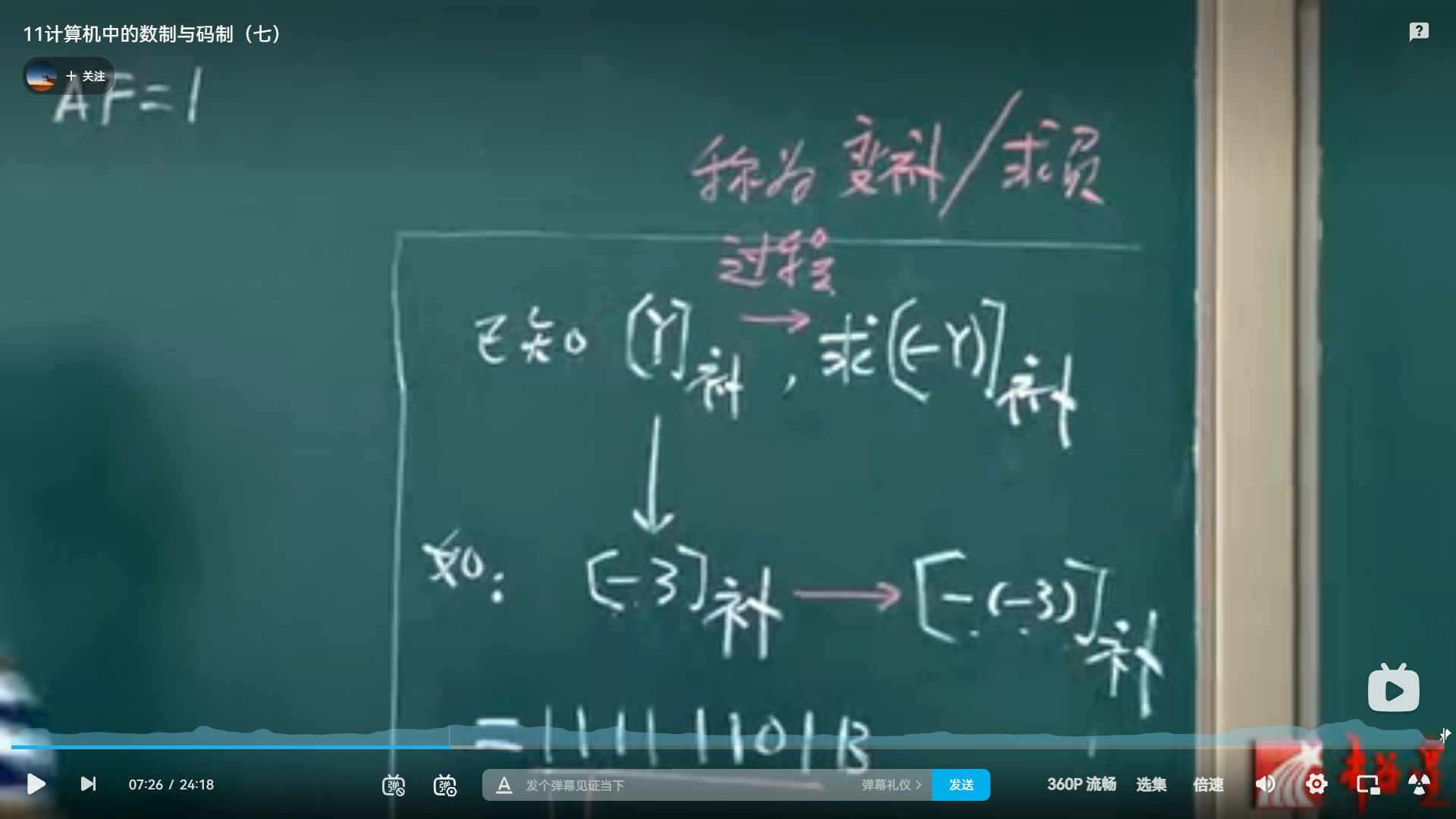

数制与码制(七)

补码运算规则(补充)

补码的补码就是原码

变补(求负)

[X]变补 = [-X]补,变补类似补码,变补是全部取反再加1,无符号位一说

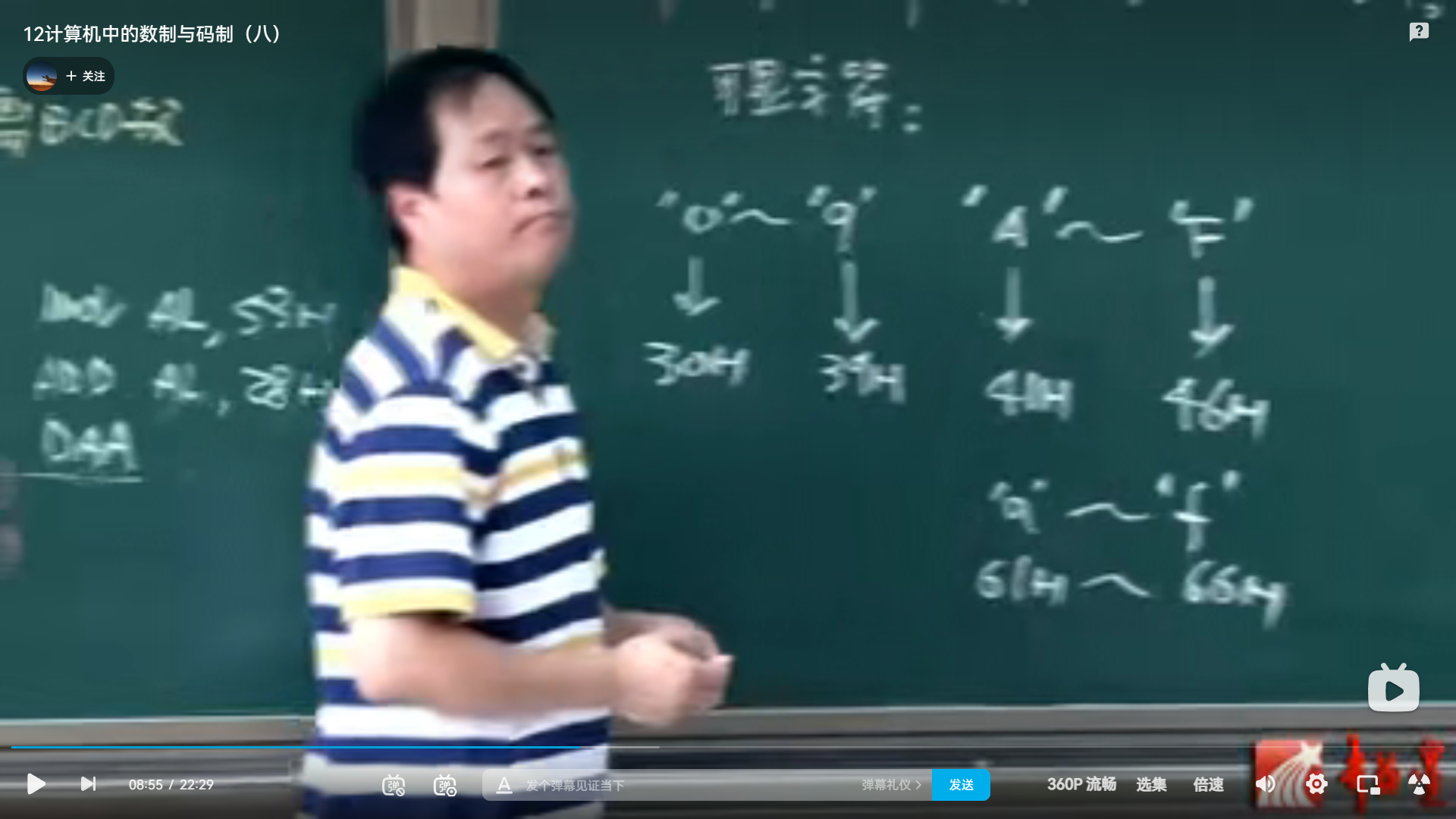

BCD码

BCD码:用四个二进制位表示一个十进制数字;最常用的是8421 BCD码;

- 压缩型BCD码

一个字节可存放一个两位十进制数,其中高四位存放十位数字,低四位存放个位数字。如:56的压缩型8421 BCD码是0101 0110;

- 非压缩型BCD码

一个字节可存放一个一位十进制数,其中高字节为0,低字节的低四位存放个位。如:5的非压缩型BCD码是0000 0101,必须存放在一个字节中,56的非压缩型BCD码是00000101 00000110,必须存放在一个字中。

BCD码的修正

- 对低四位的修正

- 查看低四位的数值是否大于9,如果大于,就+6强制让其进位,低四位的就得到了正确值。

- 查看低四位是否向高四位有进位,查看标志寄存器AF,如果有,就+6补上其进位多进走的6,低四位就得到了正确的值

- 对高四位的修正

- 查看高四位的数值是否大于9,如果大于,就+6强制让其进位,高四位的就得到了正确值。

- 查看高四位是否向不存在的第五位有进位,查看进位标志位CF,如果有,就+6补上其进位多进走的6,高四位就得到了正确的值

数制与码制(八)

ASCII码

-

数字字符转数字

-30H -

大写字符转小写

OR 20H -

小写字符转大写

AND 0DFH

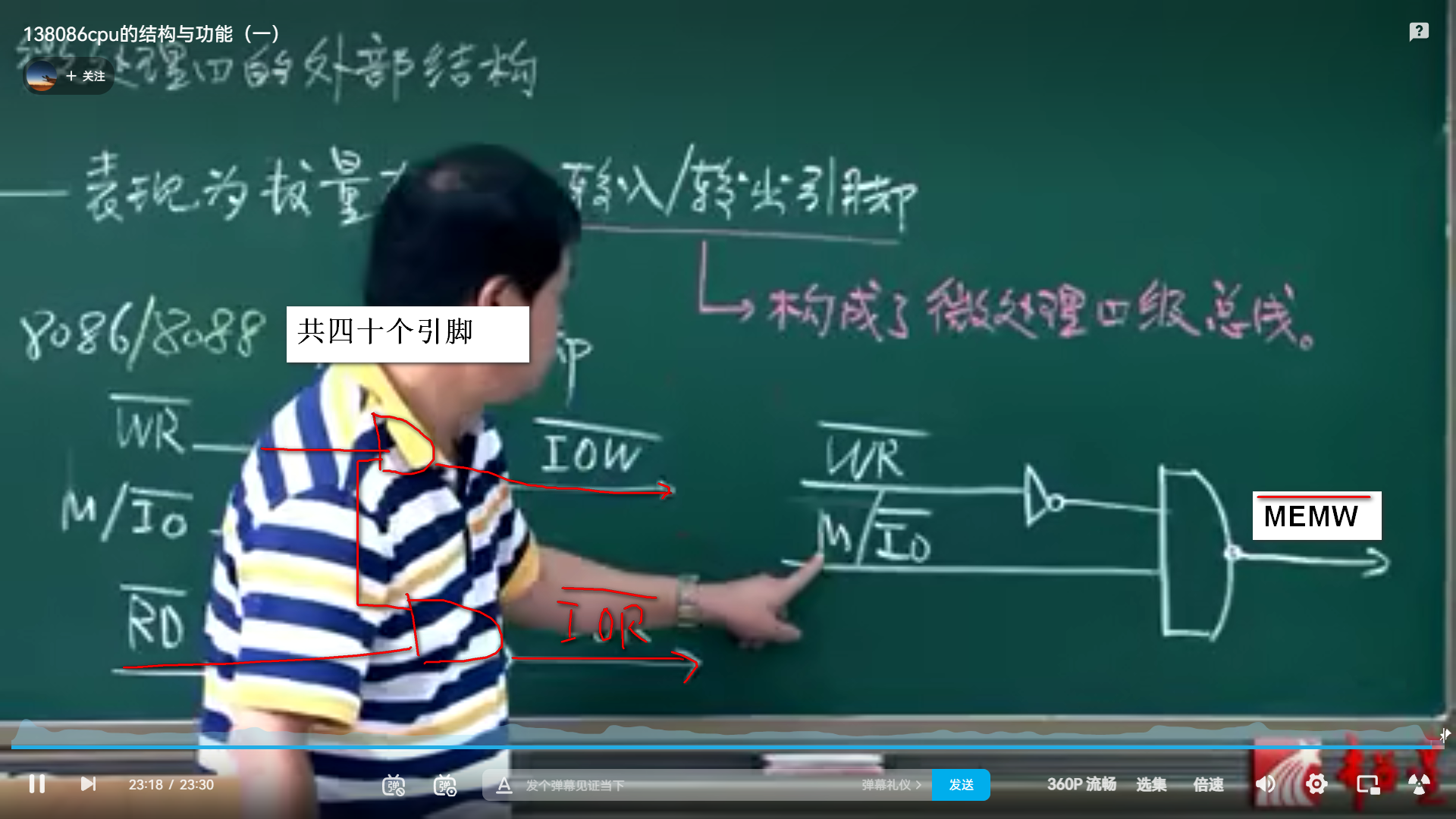

CPU结构与功能(一)

CPU结构与功能(二)

CPU结构与功能(三)

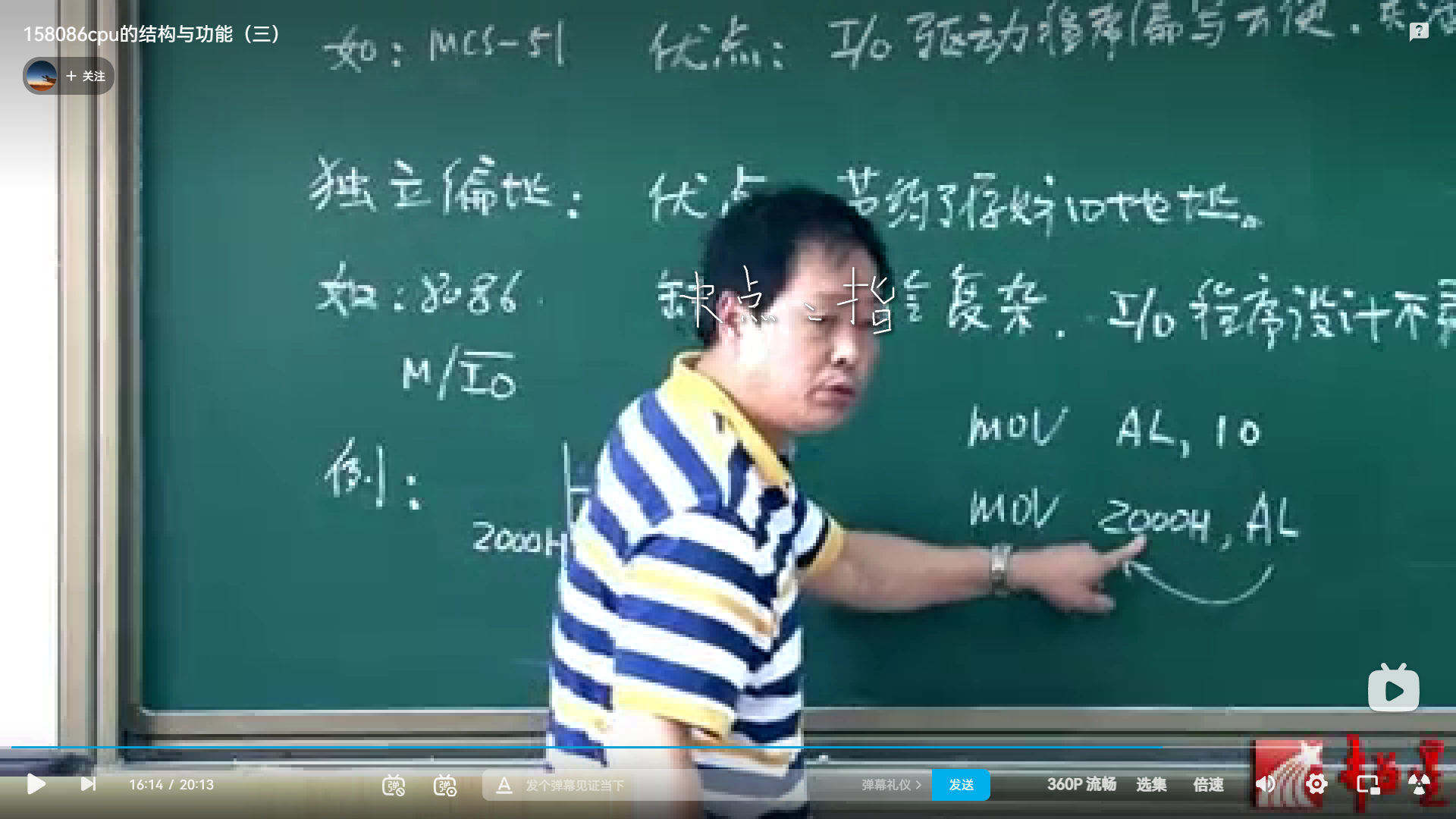

独立编址与统一编址

在不同的系统中,I/O端口的地址编排有两种形式:

存储器统一编址和I/O独立编址。

- 存储器统一编址(存储器映像编址):

- 优点

- 驱动程序设计简单

- CPU中对存储器可用的寻址方式对I/O同样可用

- 缺点

- 占用了存储器的地址空间

- 优点

- I/O独立编址:

- 优点

- 不占用内存空间

- 缺点

- 相对而言,指令变得复杂了

- 寻址方式少了

- 优点

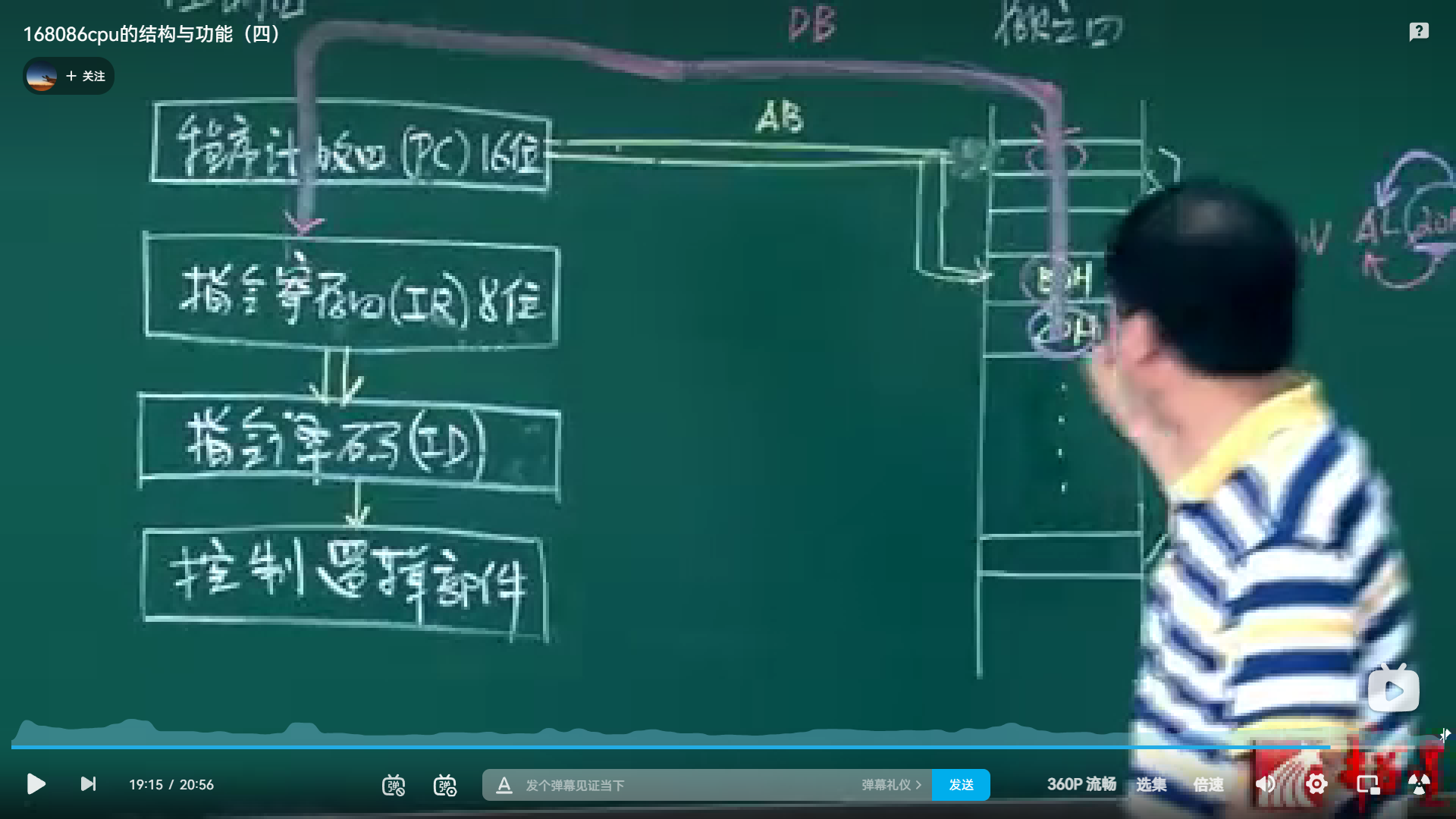

CPU结构与功能(四)

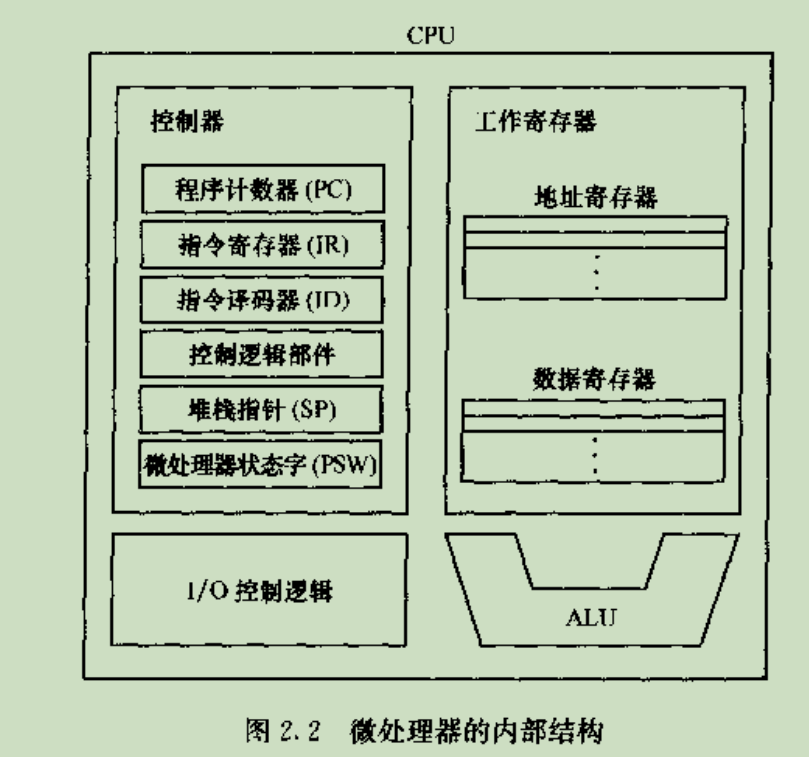

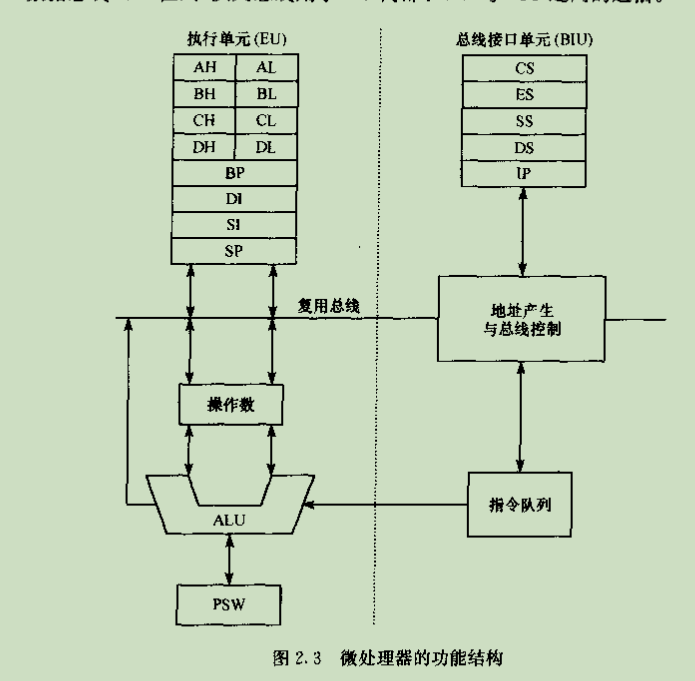

典型的CPU的内部结构

CPU结构与功能(五)

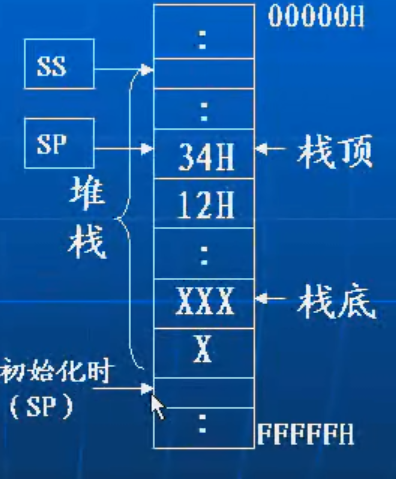

堆栈

8086/8088CPU的内部结构

CPU结构与功能(六)

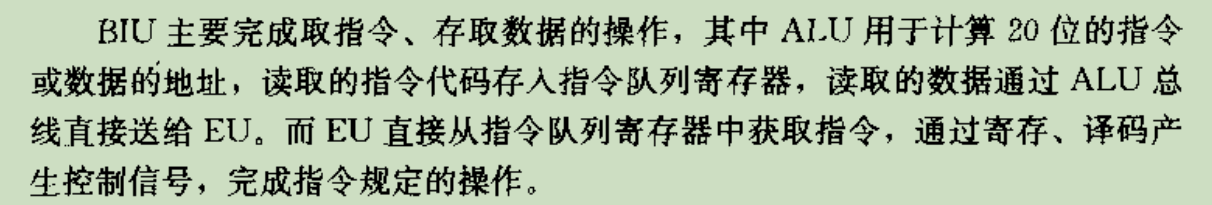

BIU和EU

通用寄存器中数据寄存器

CPU结构与功能(七)

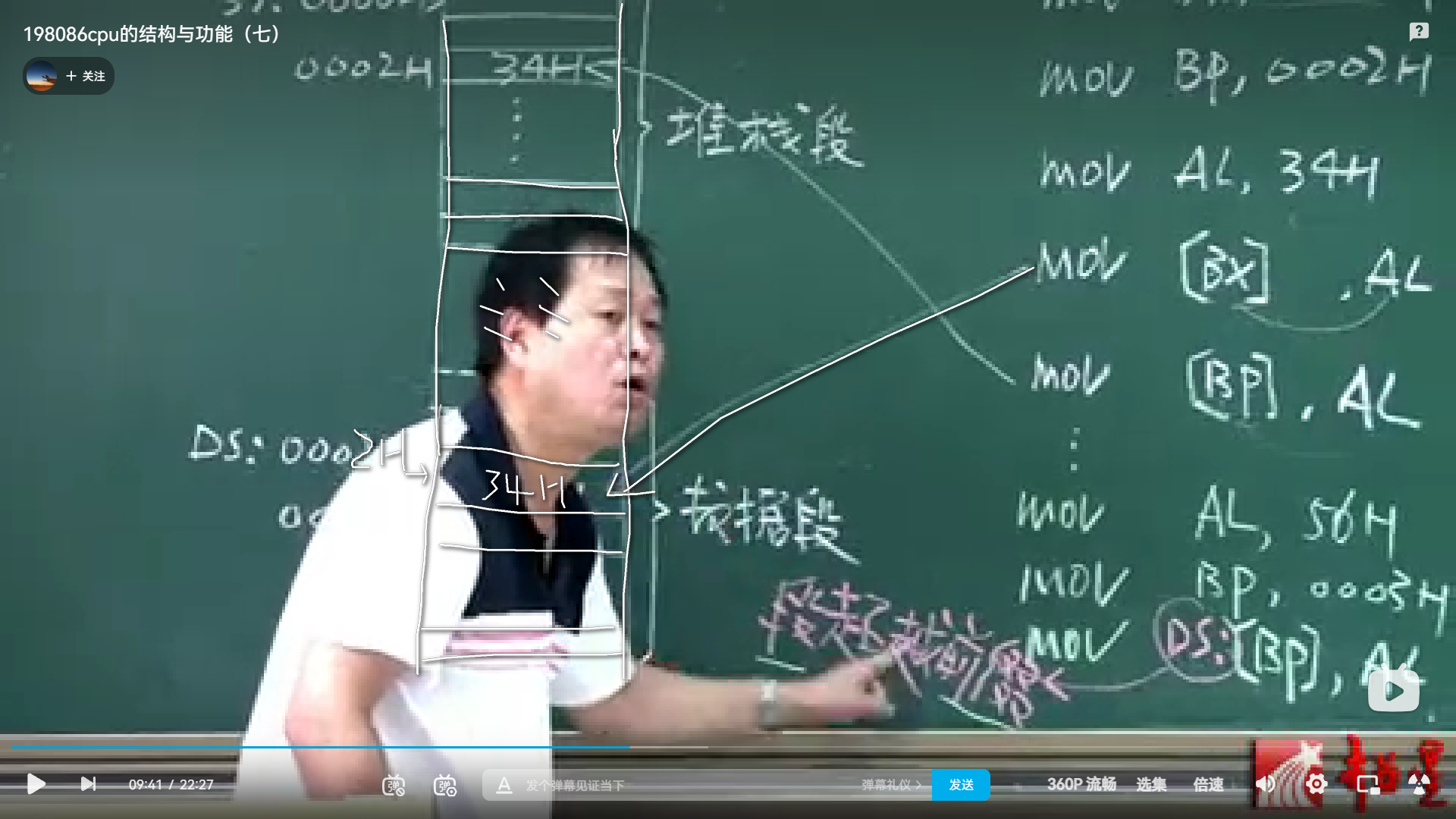

BX和BP指示偏移地址时区别

用户编程中指示偏移地址的寄存器有BX、BP、SI、DI.

在存储器单元寻址方式中,使用BX、SI、DI指示偏移地址时,隐含引用的是数据段DS。

若使用BP指示偏移地址,隐含引用的是堆栈段SS。

通用寄存中变址寄存器

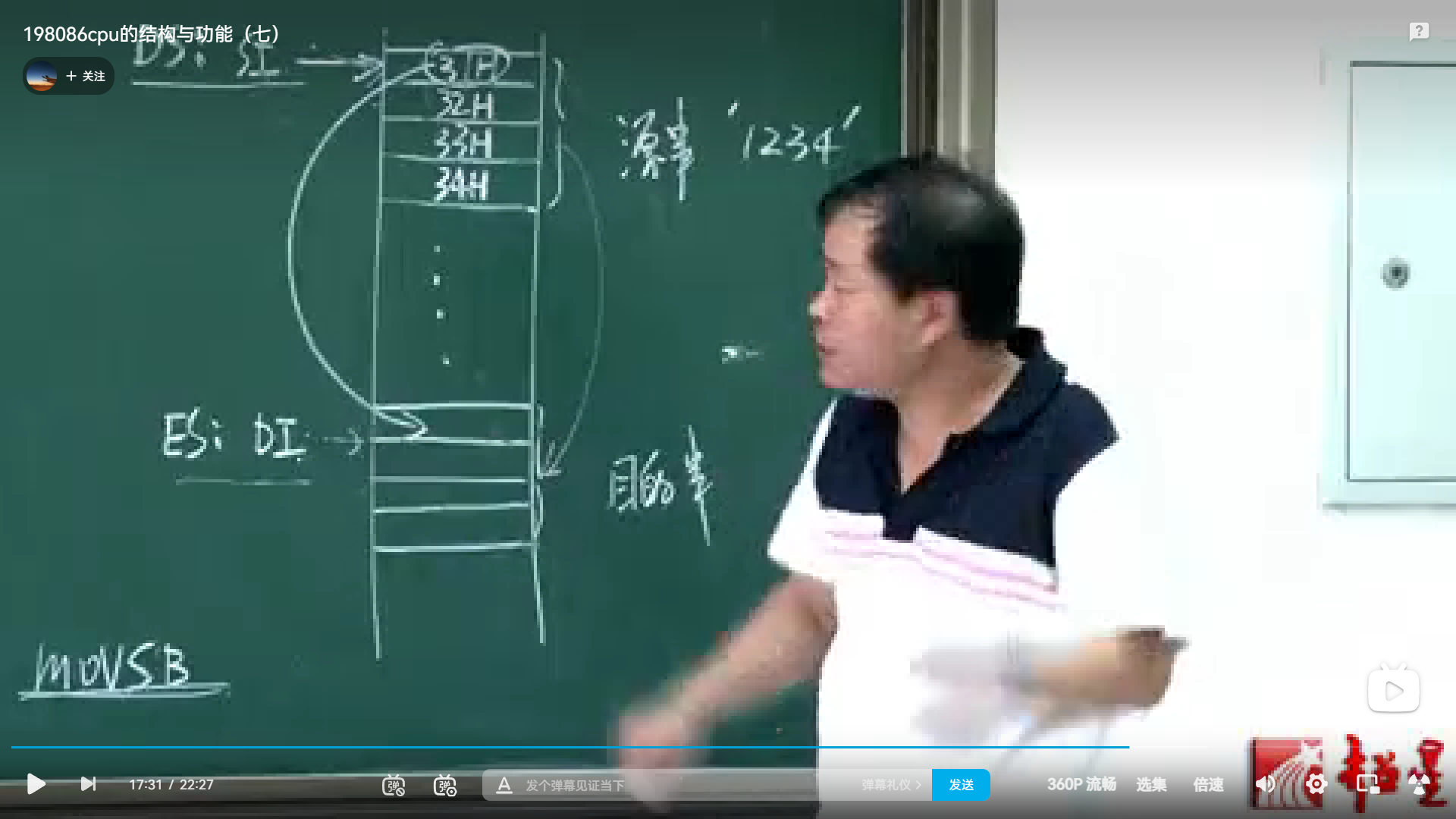

SI、DI和字符串操作指令

SI是源变址寄存器,DI是目的变址寄存器。可以用来存放数据、地址,功能类似、用法类似、一般使用哪个都可以。

但需要注意的是:在串处理指令中,SI用作隐含的源串地址,默认在DS中;DI用做隐含的目的串地址,默认在ES中;此时不能混用。

段寄存器

CPU结构与功能(八)

CS 寄存器 和 IP 寄存器

CS和IP是8086CPU中两个关键的寄存器,它们指示了CPU当前要读取指令的地址。 CS : 代码段寄存器;IP : 指令指针寄存器。 在8086机中,任意时刻,CPU将CS:IP指向的内容当作指令来执行。

控制寄存器

PSW中的控制标志

CPU结构与功能(九)

CPU结构与功能(十)

8086系统中字的“对准存放”

读取一个字时,如果该字从偶地址开始存放,那么cpu只需要访问一次存储器即可。然而,如果该字从奇地址开始存放,cpu需要先访问奇地址存储体,把字的低字节取出,再访问偶地址存储体,把字的高字节取出,即访问了两次,降低了访问速度。

-

问题:

8086CPU中有20位地址线,寄存器却只有16位,为了寻址位的地址,就需要提出解决办法。

-

解决方法:

把存储器分成16份,每份64kb,即位,每一份就是一个逻辑段,每一段的起始地址必须可以被16整除。

CPU结构与功能(十一)

物理地址(PA)的形成

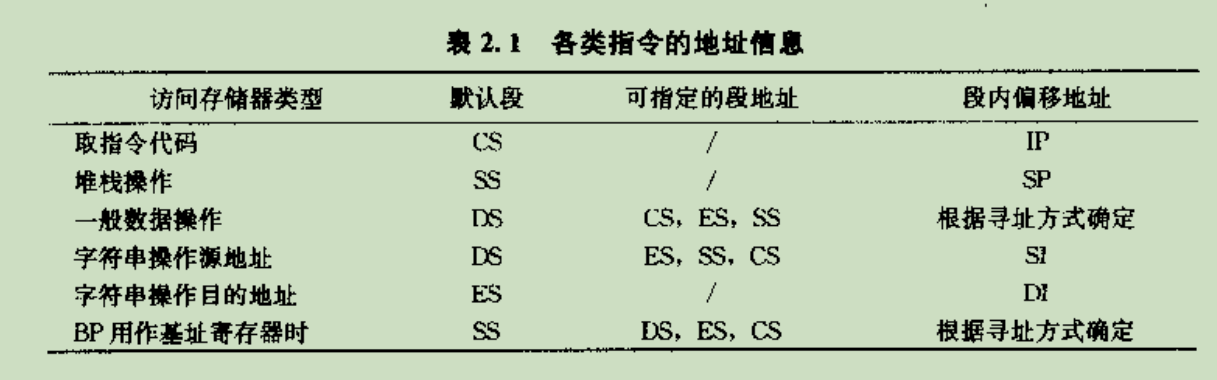

各类指令的地址信息

CPU指令系统(一)

使用DOSBox编写汇编程序

debug命令:

标志寄存器:

CPU指令系统(二)

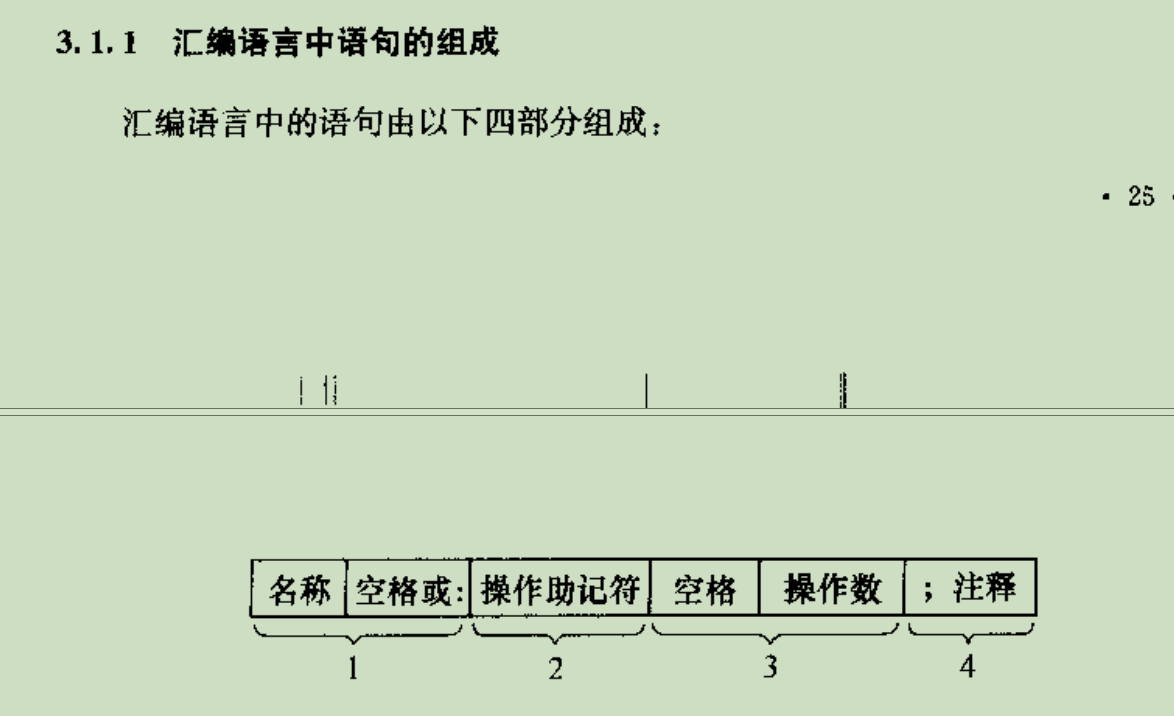

汇编语言中语句的组成

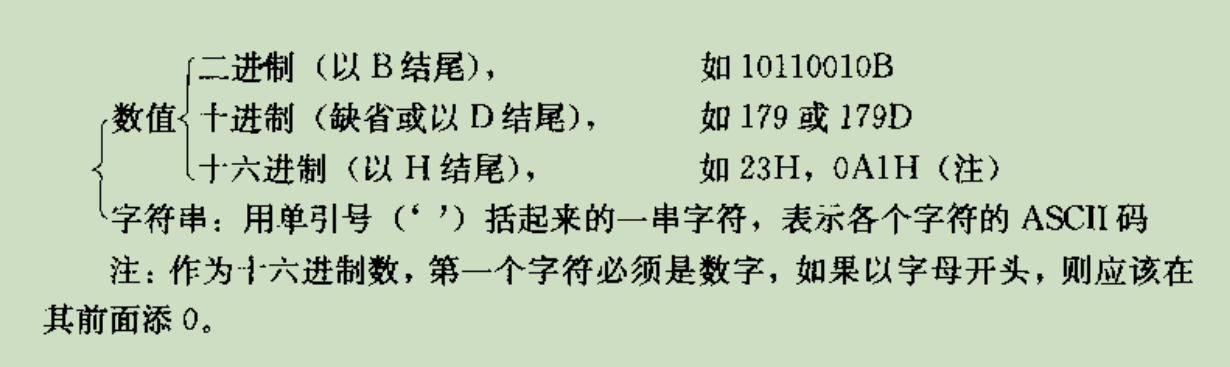

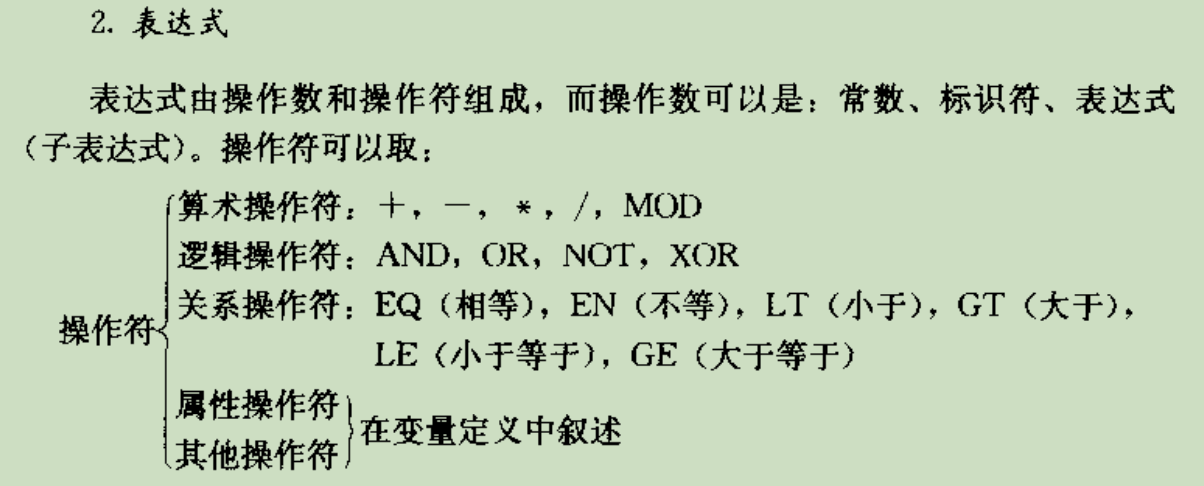

汇编语言中的常数与表达式

-

常数

-

表达式

关系运算的真值是全1,假是全0。

CPU指令系统(三)

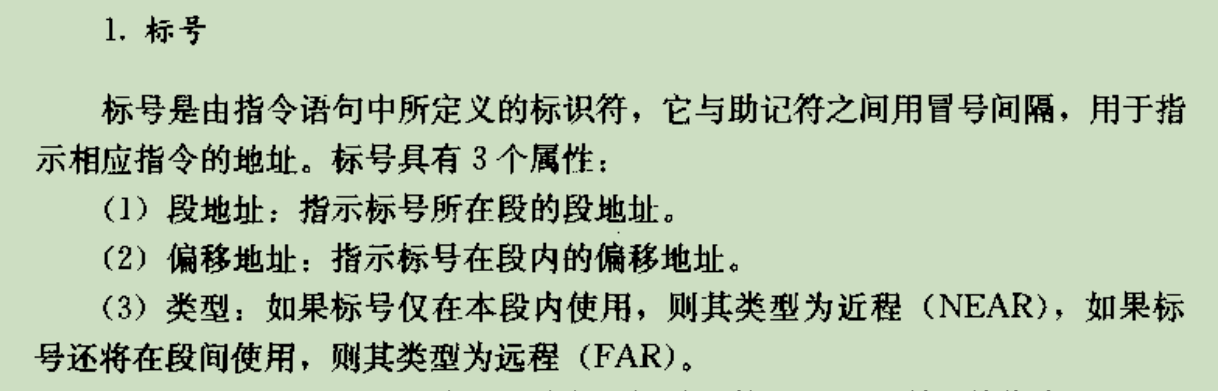

标号

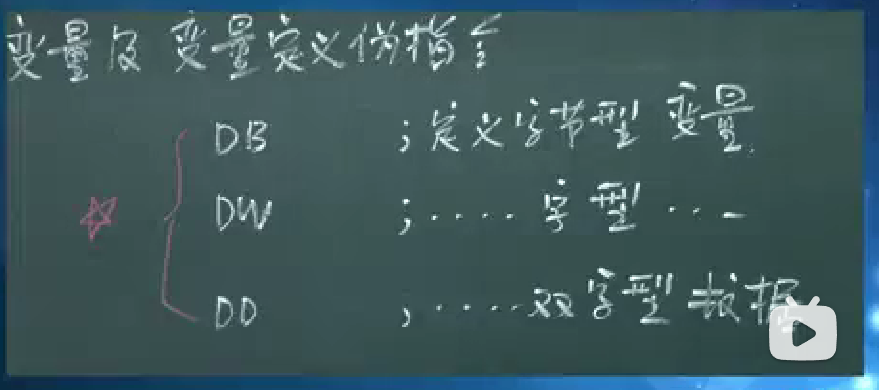

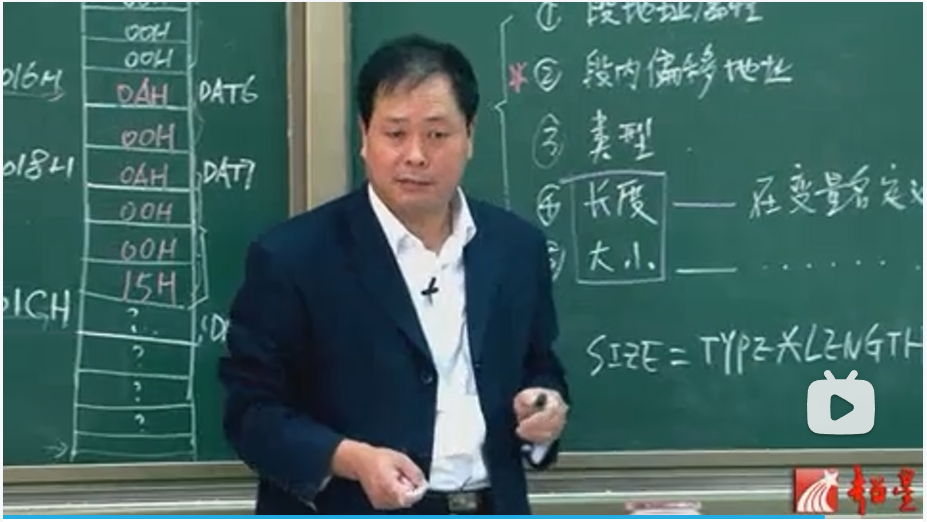

变量及变量定义伪指令

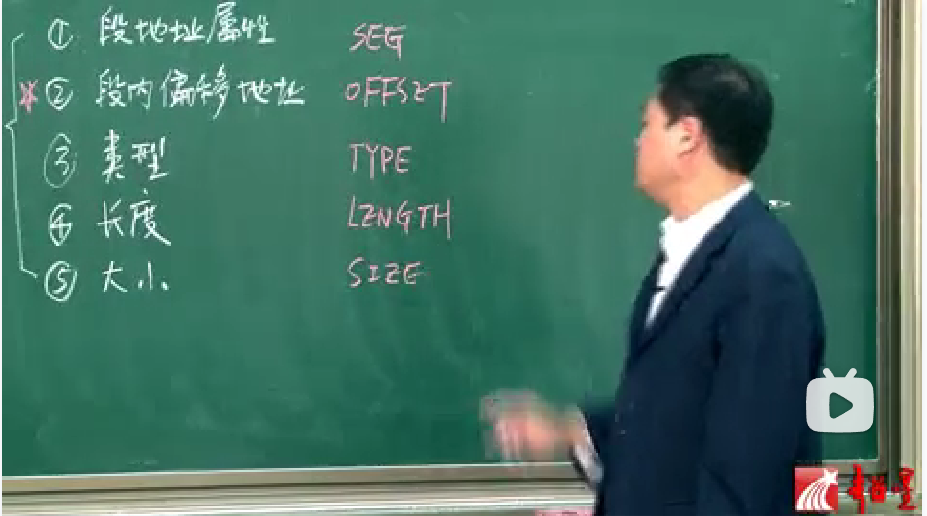

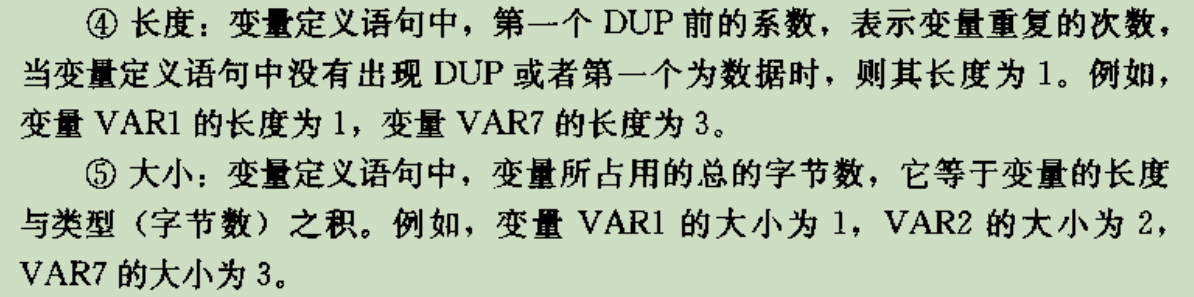

变量的属性

汇编语言中“$”的作用

“$” 是汇编语言中的一个预定义符号,等价于当前正汇编到的段的当前偏移值。

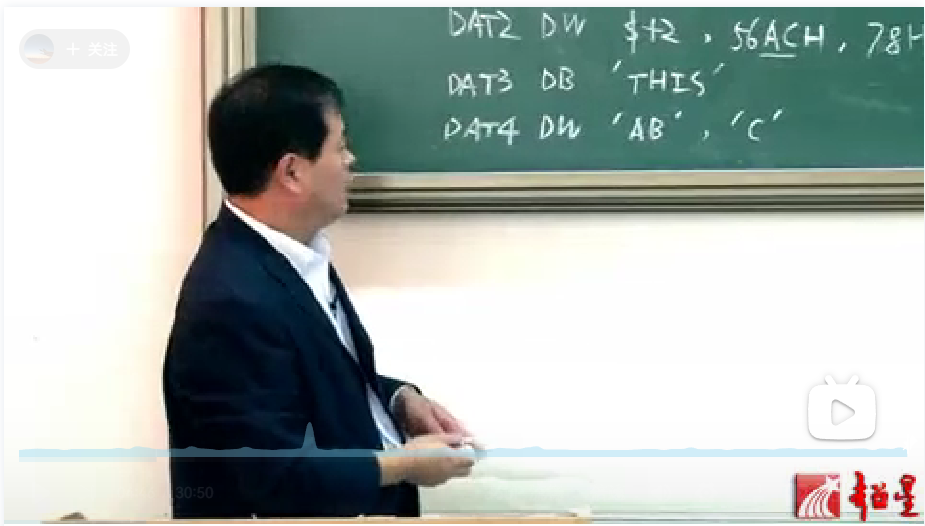

CPU指令系统(四)

汇编语言DB定义字符串和DW定义字符串

-

使用DB作为数据类型的时候,字符串长度不受限制,默认字符串的每一个字符占一个字节,并且存储过程中,是按照一个字符占一个字节的方式,顺序依次存储的。

源程序如下:

1

2

3

4assume ds:data

data segment

data1 db 'abcchsadhkjhsfaksaskhasf'

data ends对应的内存单元,原来是这样的:

1

2

30710:0000 00 00 00 00 00 00 00 00-00 00 00 00 00 00 00 00 ................

0710:0010 00 00 00 00 00 00 00 00-00 00 00 00 00 00 00 00 ................

0710:0020 00 00 00 00 00 00 00 00-00 00 00 00 00 00 00 00 ................放入代码段数据之后是:

1

2

30710:0000 61 62 63 63 68 73 61 64-68 6B 6A 68 73 66 61 6B abcchsadhkjhsfak

0710:0010 73 61 73 6B 68 61 73 66-00 00 00 00 00 00 00 00 saskhasf........

0710:0020 00 00 00 00 00 00 00 00-00 00 00 00 00 00 00 00 ................ -

使用

dw数据类型,则最多存储2个字节。

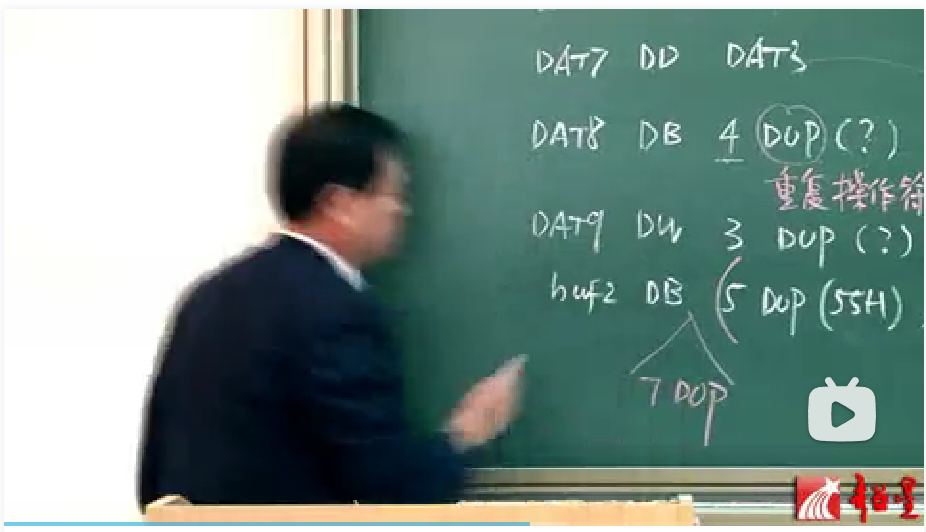

操作符dup

dup是一个操作符,在汇编语言中同dw、db、dd等一样,也是由编译器识别处理的符号。它是和db、dd、dw等数据定义伪指令配合使用的,用来进行数据的重复。

1 | db 3 dup (0) ;定义了三个字节,相当于db 0,0,0 这个0有多大是通过前面的db确定 |

dup操作符支持嵌套。

汇编中的PTR含义/用法

ptr – pointer (既指针)得缩写。

汇编里面 ptr 是规定 的 字 (既保留字),是用来临时指定类型的。